# PY32F403

# 32-bit ARM® Cortex® M4F Microcontroller

# Reference manual

Puya Semiconductor (Shanghai) Co., Ltd

# **Contents**

|    |                   | tion                                                      |    |

|----|-------------------|-----------------------------------------------------------|----|

| 2. | System a          | and memory architecture                                   | 16 |

| 2  | .1. Arm           | ® Cortex®-M4 Processor Introduction                       | 16 |

| 2  | .2. Syst          | tem architecture                                          | 16 |

|    | 2.2.1.            | I bus                                                     | 17 |

|    | 2.2.2.            | D_bus                                                     | 17 |

|    | 2.2.3.            | S bus                                                     | 17 |

|    | 2.2.4.            | DMA1/DMA2 BUS                                             | 17 |

|    | 2.2.5.            | Bus Matrix                                                |    |

|    | 2.2.6.            | AHB/APB bus bridge                                        | 18 |

| 2  | .3. Men           | nory Organisation                                         | 18 |

|    | 2.3.1.            | Introduction                                              | 18 |

|    | 2.3.2.            | Memory Map                                                | 18 |

| 2  | .4. Emb           | pedded SRAM                                               | 21 |

| 2  |                   | pedded FLASH                                              |    |

|    |                   | Segments                                                  |    |

| 2  | .7. Star          | t-up configuration                                        |    |

|    | 2.7.1.            | Embedded start-up program                                 | 23 |

|    | 2.7.2.            | Physical remapping                                        |    |

| 3. |                   | ed Flash Memory                                           |    |

| 3  |                   | oduction                                                  |    |

|    | 3.1.1.            | Main features                                             |    |

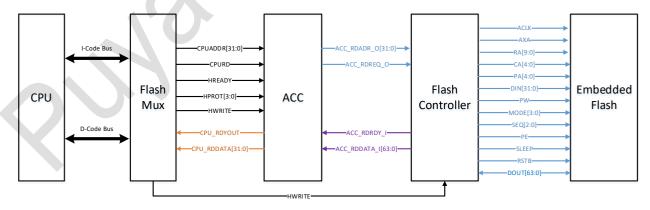

|    | 3.1.2.            | Module block diagram                                      |    |

| 3  |                   | ctional description                                       |    |

|    | 3.2.1.            | Flash memory structure                                    |    |

|    | 3.2.2.            | Flash memory read operations and access latencies         |    |

|    | 3.2.3.            | Adaptive Real-Time Memory Accelerator™ (ART Accelerator™) | 27 |

|    | 3.2.4.            | Erasing and programming operations                        |    |

|    | 3.2.5.            | Flash erase operations                                    |    |

|    | 3.2.6.            | Flash memory write operations                             |    |

|    | 3.2.7.            | Flash option bytes                                        |    |

|    | 3.2.8.            | Flash configuration bytes                                 |    |

| 2  | 3.2.9.<br>.3. Rea | Flash memory interrupts                                   |    |

| 3  | .s. keg<br>3.3.1. | FLASH access control register(FLASH_ACR)                  |    |

|    | 3.3.1.            | FLASH key register(FLASH_KEYR)                            |    |

|    | 3.3.3.            | FLASH option key register(FLASH_OPTKEYR)                  |    |

|    | 3.3.4.            | FLASH status register(FLASH_SR)                           |    |

|    | 3.3.5.            | FLASH control register(FLASH_CR)                          |    |

|    | 3.3.6.            | FLASH option register(FLASH_OPTR)                         |    |

|    | 3.3.7.            | FLASH WRP register(FLASH_WRPR)                            |    |

|    | 3.3.8.            | FLASH sleep time config register(FLASH_STCR)              |    |

|    | 3.3.9.            | FLASH TS0 register(FLASH_TS0)                             |    |

|    | 3.3.10.           | FLASH TS1 register(FLASH_TS1)                             |    |

|    | 3.3.11.           | FLASH TS2P register(FLASH_TS2P)                           |    |

|    | 3.3.12.           | FLASH TPS3 register(FLASH_TPS3)                           |    |

|    | 3.3.13.           | FLASH TS3 register(FLASH_TS3)                             |    |

|    | 3.3.14.           | FLASH ERASE TPE register(FLASH_ERSTPE)                    |    |

|    | 3.3.15.           | FLASH PROGRAM TPE register(FLASH_PRGTPE)                  |    |

|    | 3.3.16.           | FLASH PRE-PROGRAM TPE register (FLASH_PRETPE)             |    |

|    | 3.3.17.           | FLASH register map                                        |    |

| 4. |                   | ontrol (PWR)                                              |    |

|    |                   | ctional description                                       |    |

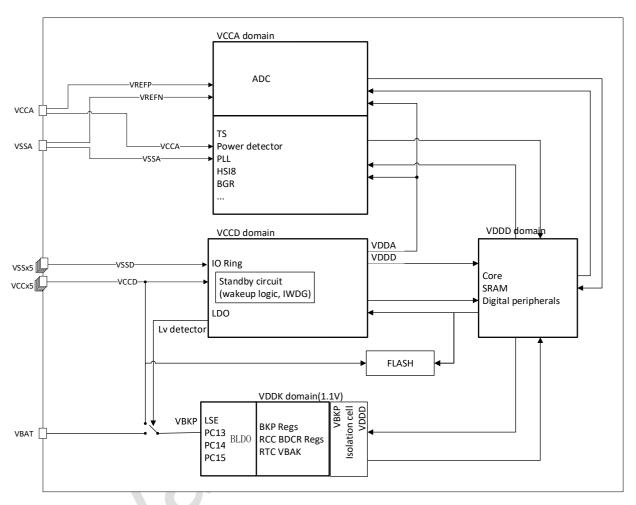

|    | 4.1.1.            | Power supply structure                                    |    |

|    | 4.1.2.            | System Low Power Mode                                     |    |

| 4  |                   | ister description (base address 0x4000_7000)              |    |

|    | 4.2.1.            | power control register (PWR_CR) (0x00)                    |    |

|    | 4.2.2.            | power control/status registers (PWR_CSR)(0x04)            |    |

|    | 4.2.3.            | PWR Register map                                          |    |

| 5. |                   | nd clock control (RCC)                                    |    |

|    |                  | cription of the reset function                                                     |      |

|----|------------------|------------------------------------------------------------------------------------|------|

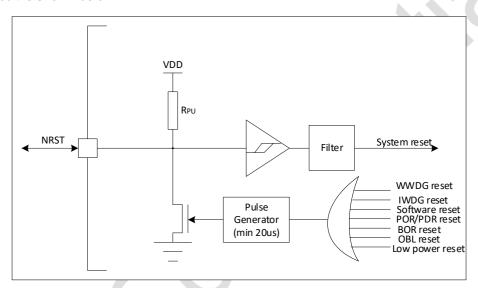

|    | 5.1.1.           | System reset                                                                       |      |

|    | 5.1.2.           | power reset                                                                        |      |

|    | 5.1.3.<br>5.1.4. | Unified handling of resets other than backup domain resets                         |      |

|    |                  | ctional description of the clock                                                   |      |

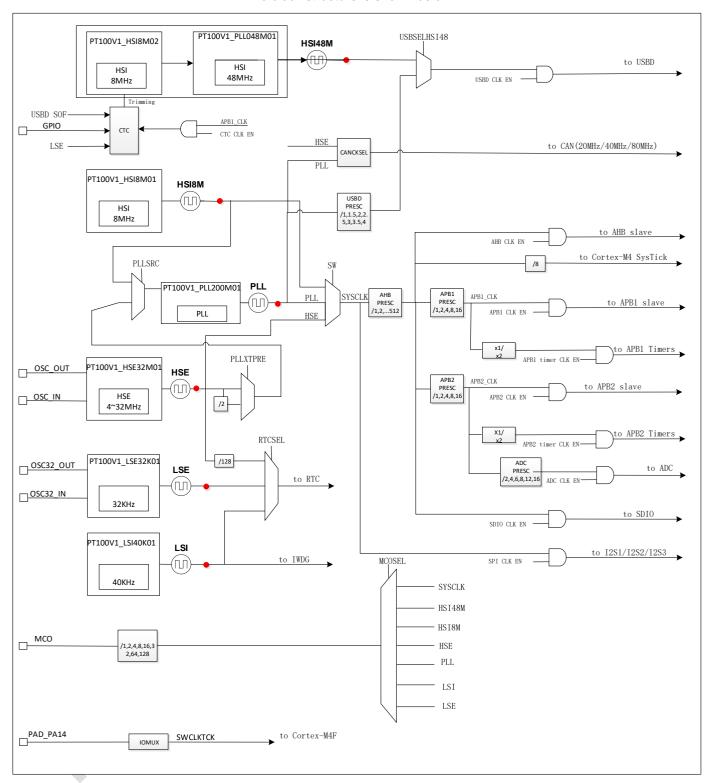

|    | 5.2.1.           | Clock structure                                                                    |      |

|    | 5.2.2.           | Clock source (clock signal and parameters subject to analogue module requirements) | . 71 |

|    | 5.3. Reg         | ister (base: 0x40021000)                                                           | . 73 |

|    | 5.3.1.           | Clock Control Register (RCC_CR)                                                    | . 73 |

|    | 5.3.2.           | Clock Configuration Register (RCC_CFGR)                                            | . 75 |

|    | 5.3.3.           | Clock interrupt register (RCC_CIR)                                                 | . 78 |

|    | 5.3.4.           | APB2 Peripheral Reset Register (RCC_APB2RSTR)                                      | . 80 |

|    | 5.3.5.           | APB1 Peripheral Reset Register (RCC_APB1RSTR)                                      | . 82 |

|    | 5.3.6.           | AHB1 Peripheral Clock Enable Register (RCC_AHB1ENR)                                | . 84 |

|    | 5.3.7.           | APB2 Peripheral Clock Enable Register (RCC_APB2ENR)                                |      |

|    | 5.3.8.           | APB1 Peripheral Clock Enable Register (RCC_APB1ENR)                                |      |

|    | 5.3.9.           | RTC domain control register (RCC_BDCR)                                             | . 88 |

|    | 5.3.10.          | Control/status register (RCC_CSR)                                                  |      |

|    | 5.3.11.          | Clock Reset Configuration Register 1 (RCC_CFGR1)                                   |      |

|    | 5.3.12.          | AHB1 peripheral reset register (RCC_AHB1RSTR)                                      |      |

|    | 5.3.13.          | AHB2 peripheral reset register (RCC_AHB2RSTR)                                      |      |

|    | 5.3.14.          | AHB2 peripheral clock enable register (RCC_AHB2ENR)                                |      |

|    | 5.3.15.          | Clock Reset Configuration Register 2 (RCC_CFGR2)                                   |      |

|    | 5.3.16.          | RCC register map                                                                   |      |

| 6. | Backup           | register (BKP)                                                                     | . 97 |

|    | 6.1. Intro       | oduction                                                                           |      |

|    | 6.1.1.           | Main features                                                                      |      |

|    |                  | ctional description                                                                |      |

|    | 6.2.1.<br>6.2.2. | Intrusion Detection                                                                |      |

|    |                  | P register (base address = 0x40006C00)                                             |      |

|    | 6.3.1.           | Backup Data Register (BKP_DRx) (x=142)                                             |      |

|    | 6.3.2.           | RTC Clock Calibration Register (BKP_RTCCR)                                         |      |

|    | 6.3.3.           | Backup control register (BKP_CR)                                                   |      |

|    | 6.3.4.           | Backup control/status register (BKP_CSR)                                           |      |

|    | 6.3.5.           | BKP register map                                                                   |      |

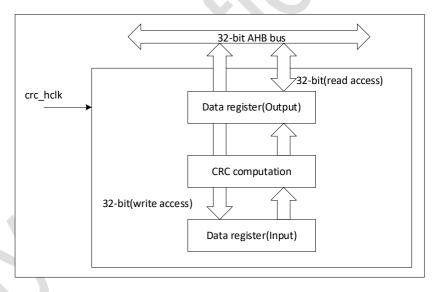

| 7. |                  | culation unit (CRC)                                                                |      |

|    |                  | oduction                                                                           |      |

|    | 7.2. Maii        | n features of CRC                                                                  | 115  |

|    |                  | cription of the CRC function                                                       |      |

|    | 7.3.1.           | CRC block diagram                                                                  |      |

|    |                  | C register                                                                         |      |

|    | 7.4.1.           |                                                                                    |      |

|    | 7.4.2.           | Independent data register ( CRC_IDR)                                               |      |

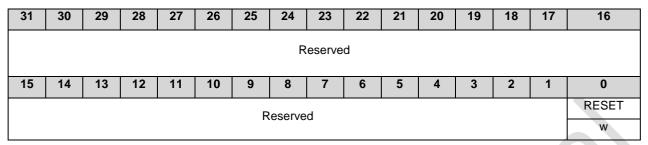

|    | 7.4.3.           | Control register (CRC_CR)                                                          |      |

| 8. | 7.4.4.           | CRC register map                                                                   |      |

| о. |                  | -purpose I/O(GPIO)                                                                 |      |

|    |                  | n features                                                                         |      |

|    |                  | ctional descriptions                                                               |      |

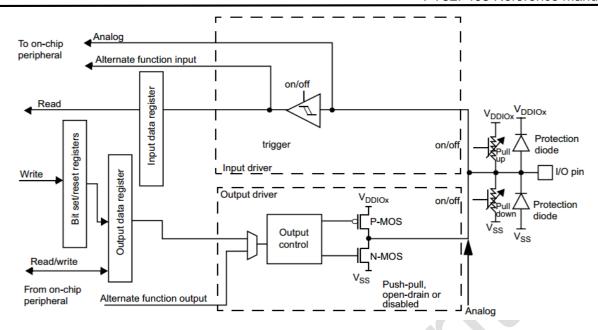

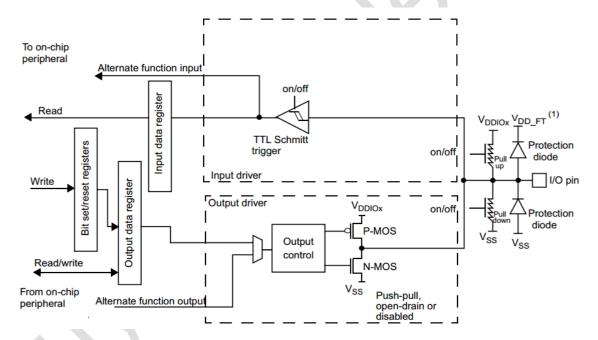

|    | 8.3.1.           | General-purpose I/O (GPIO)                                                         |      |

|    | 8.3.2.           | I/O Pin Multiplexer and Mapping                                                    |      |

|    | 8.3.3.           | I/O Port Control Register                                                          |      |

|    | 8.3.4.           | I/O Port Data Register                                                             |      |

|    | 8.3.5.           | I/O Data Bit Operations                                                            |      |

|    | 8.3.6.           | GPIO Locking Mechanisms                                                            |      |

|    | 8.3.7.           | I/O Multiplexed Function Input/Output Mode Configuration                           |      |

|    | 8.3.8.           | External interrupt/wake-up lines                                                   |      |

|    | 8.3.9.           | I/O input configuration                                                            | 124  |

| 8.3.10.   | Output configuration                                         |     |

|-----------|--------------------------------------------------------------|-----|

| 8.3.11.   | Configuration of the multiplexing function                   |     |

| 8.3.12.   | Analogue configuration                                       | 124 |

| 8.3.13.   | HSE or LSE Pins Configured as GPIO                           |     |

| 8.3.14.   | BKP Area GPIO Usage                                          |     |

|           | gister Descriptions                                          |     |

| 8.4.1.    | GPIO Port Mode Register (GPIOx_MODER) (x= AE)                |     |

| 8.4.2.    | GPIO Port Output Type Register (GPIOx_OTYPER) (x= AE)        |     |

| 8.4.3.    | GPIO Port Output Speed Register (GPIOx_OSPEEDR) (x= AE)      |     |

| 8.4.4.    | GPIO Port Pull-Up/Pull-Down Register (GPIOx_PUPDR) (x= AE)   |     |

| 8.4.5.    | GPIO Port Input Data Register (GPIOx_IDR) (x= AE)            |     |

| 8.4.6.    | GPIO Port Output Data Register (GPIOx_ODR) (x= AE)           |     |

| 8.4.7.    | GPIO Port Reset/Reset Register (GPIOx_BSRR) (x= AE)          |     |

| 8.4.8.    | GPIO Port Configuration Lock Register (GPIOx_LCKR) (x= AE)   |     |

| 8.4.9.    | GPIO Multiplexing Function Low Register (GPIOx_AFRL) (x= AE) | 129 |

| 8.4.10.   | GPIO Multiplexing High Register (GPIOx_AFRH) (x= AE)         | 130 |

| 8.4.11.   | GPIO Port Bit Reset Register (GPIOx_BRR) (x= AE)             | 130 |

| 8.4.12.   | GPIO register address map                                    | 131 |

| 9. System | configuration controller (SYSCFG)                            | 135 |

|           | erview                                                       |     |

| 9.2. SY   | SCFG register (baseaddr=0x40010000)                          | 135 |

| 9.2.1.    | SYSCFG configuration register 1 (SYSCFG_CFGR1)               | 135 |

| 9.2.2.    | SYSCFG configuration register 2 (SYSCFG_CFGR2)               | 136 |

| 9.2.3.    | SYSCFG configuration register 3 (SYSCFG_CFGR3)               | 137 |

| 9.2.4.    | SYSCFG configuration register 4 (SYSCFG_CFGR4)               |     |

| 9.2.5.    | SYSCFG configuration register 5 (SYSCFG_CFGR5)               |     |

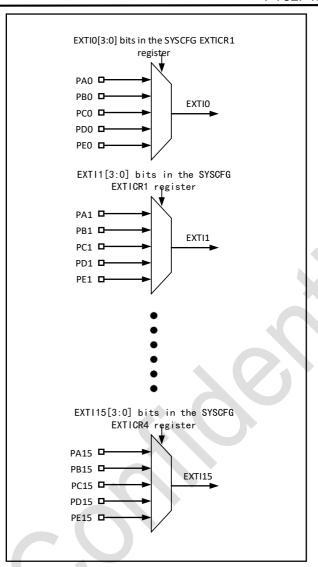

| 9.2.6.    | External interrupt configuration register 1 (SYS_EXTICR1)    |     |

| 9.2.7.    | External Interrupt Configuration Register 2 (SYS_EXTICR2)    |     |

| 9.2.8.    | External Interrupt Configuration Register 3 (SYS_EXTICR3)    |     |

| 9.2.9.    | External Interrupt Configuration Register 4 (SYS_EXTICR4)    | 142 |

| 9.2.10.   | GPIOA Filter Enable (PA_ENS)                                 | 143 |

| 9.2.11.   | GPIOB Filter Enable (PB_ENS)                                 | 143 |

| 9.2.12.   | GPIOC filter enable (PC_ENS)                                 |     |

| 9.2.13.   | GPIOD filter enable (PD_ENS)                                 |     |

| 9.2.14.   | GPIOE Filter Enable (PE_ENS)                                 |     |

| 9.2.15.   | GPIO analogue channel enable (GPIO_ENA)                      |     |

| 9.2.16.   | Timer clock extension control (TIM_CLK_EXT)                  |     |

| 9.2.17.   | SYSCFG register map                                          |     |

|           | controller (DMA)                                             |     |

|           | Overview                                                     |     |

| 10.1.1.   | Main features                                                |     |

| 10.2. F   | -unctional descriptions                                      |     |

| 10.2.1.   | DMA transmission                                             |     |

| 10.2.2.   | Arbiter                                                      | 152 |

| 10.2.3.   | DMA Channel                                                  |     |

| 10.2.4.   | Data transfer width/alignment/size end                       |     |

| 10.2.5.   | Error Handling                                               |     |

| 10.2.6.   | Interrupt                                                    |     |

| 10.2.7.   | 1 11 5                                                       |     |

|           | Register Descriptions (0x40020000)                           |     |

| 10.3.1.   | DMA interrupt status register (DMA_ISR)                      |     |

| 10.3.2.   | DMA Interrupt Flag Clear Register (DMA_IFCR)                 |     |

| 10.3.3.   | DMA Channel 1 Configuration Register (DMA_CCR1)              |     |

| 10.3.4.   | DMA Channel 1 Number of Data Transfers Register (DMA_CNDTR1) |     |

| 10.3.5.   | DMA Channel 1 Peripheral Address Register (DMA_CPAR1)        |     |

| 10.3.6.   | DMA Channel 1 Memory Address Register (DMA_CMAR1)            | 167 |

| 10.3.7.   | DMA Channel 2 Configuration Register (DMA_CCR2)              |     |

| 10.3.8.   | DMA Channel 2 Number of Data Transfers Register (DMA_CNDTR2) | 169 |

| 10 3 9    | DMA Channel 2 Peripheral Address Register (DMA CPAR2)        |     |

| 10.3.10.             | DMA Channel 2 Memory Address Register (DMA_CMAR2)            | 170        |

|----------------------|--------------------------------------------------------------|------------|

| 10.3.11.             | DMA Channel 3 Configuration Register (DMA_CCR3)              | 171        |

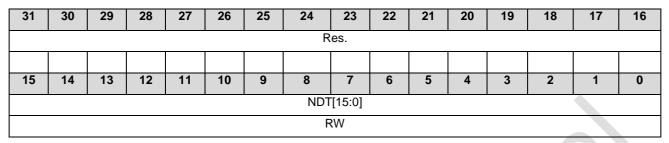

| 10.3.12.             | DMA Channel 3 Number of Data Transfers Register (DMA_CNDTR3) |            |

| 10.3.13.             | DMA Channel 3 Peripheral Address Register (DMA_CPAR3)        |            |

| 10.3.14.             | DMA Channel 3 Memory Address Register (DMA_CMAR3)            |            |

| 10.3.15.             | DMA Channel 4 Configuration Register (DMA_CCR4)              |            |

| 10.3.16.             | DMA Channel 4 Number of Data Transfers Register (DMA_CNDTR4) |            |

| 10.3.17.             | DMA Channel 4 Peripheral Address Register (DMA_CPAR4)        | 176        |

| 10.3.18.             | DMA Channel 4 Memory Address Register (DMA_CMAR4)            |            |

| 10.3.19.             | DMA Channel 5 Configuration Register (DMA CCR5)              |            |

| 10.3.20.             | DMA Channel 5 Number of Data Transfers Register (DMA_CNDTR5) |            |

| 10.3.21.             | DMA Channel 5 Peripheral Address Register (DMA_CPAR5)        |            |

| 10.3.22.             | DMA Channel 5 Memory Address Register (DMA_CMAR5)            |            |

| 10.3.23.             | DMA Channel 6 Configuration Register (DMA_CCR6)              |            |

| 10.3.24.             | DMA Channel 6 Number of Data Transfers Register (DMA_CNDTR6) |            |

| 10.3.25.             | DMA Channel 6 Peripheral Address Register (DMA_CPAR6)        |            |

| 10.3.26.             | DMA Channel 6 Memory Address Register (DMA_CMAR6)            |            |

| 10.3.27.             | DMA Channel 7 Configuration Register (DMA_CCR7)              |            |

| 10.3.27.             | DMA Channel 7 Number of Data Transfers Register (DMA_CNDTR7) |            |

| 10.3.20.             | DMA Channel 7 Peripheral Address Register (DMA_CPAR7)        |            |

| 10.3.29.             | DMA Channel 7 Memory Address Register (DMA_CMAR7)            | 105        |

| 10.3.30.             | DMA Register MapDMA Register Map                             | 180<br>186 |

|                      | pts and events                                               | 189        |

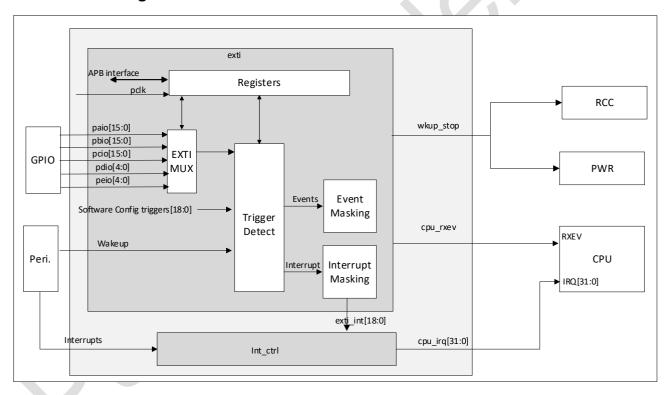

|                      | roduction                                                    |            |

| 11.1.1.              | Main features                                                |            |

| 11.1.2.              | Block diagrams of modules                                    | 189        |

|                      | ınctional description                                        |            |

|                      | Interrupt and Exception Vector Table                         |            |

|                      | External interrupt/event controller (EXIT)                   |            |

|                      | egister Descriptions                                         |            |

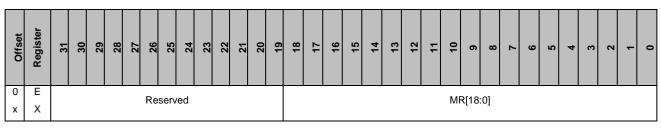

| 11.3.1.              | Interrupt Mask Registers (EXTI_IMR)                          |            |

| 11.3.2.              | Event Mask Register ( EXTI_EMR)                              |            |

| 11.3.3.              | Rising-Edge Trigger Select Register (EXTI_RTST)              |            |

| 11.3.4.              | Falling-Edge Trigger Select Register (EXTI_FTSR)             |            |

| 11.3.5.              | Software Interrupt Event Register (EXTI_SWIER)               |            |

|                      | Suspend register (EXTI_PR)                                   |            |

|                      | EXTIregister address map                                     |            |

|                      | gue/digital conversion(ADC)                                  |            |

|                      | troduction                                                   |            |

| 12.1.1.              | Main features                                                |            |

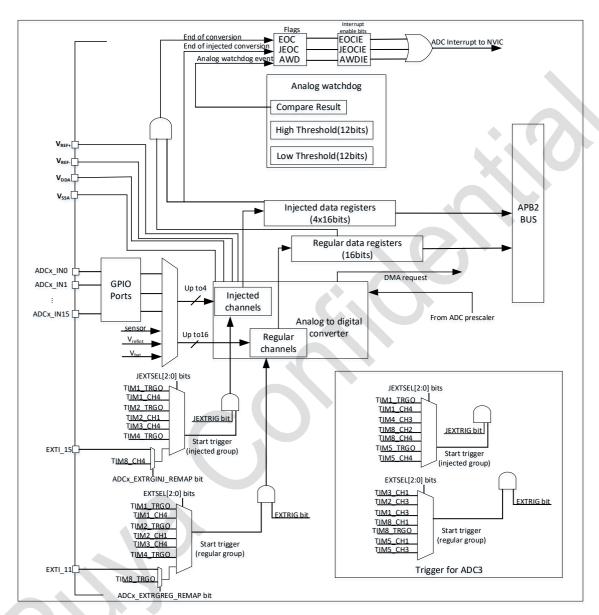

|                      | Module block diagram DC Pin Definitions                      |            |

|                      | Inctional descriptions                                       |            |

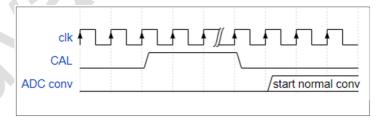

|                      | ADC calibration                                              |            |

|                      | ADC on-off control                                           |            |

|                      | ADC Clock                                                    |            |

|                      | ADC Channel Selection                                        |            |

| 12.3.5.              | Force stopping ADC                                           | 206        |

|                      | Conversion mode                                              |            |

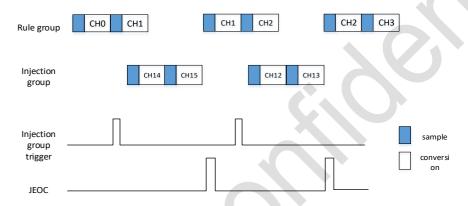

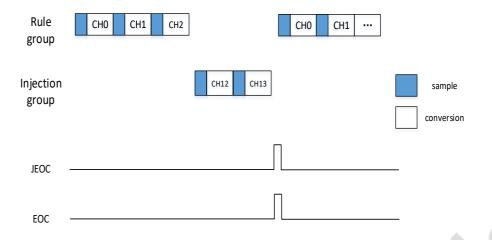

| 12.3.7.              | Injection channel management                                 |            |

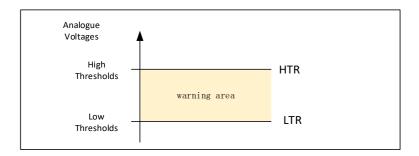

|                      | Analogue Watchdog                                            |            |

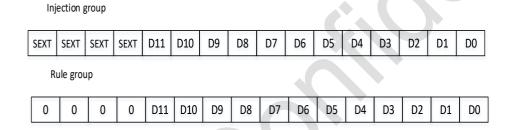

| 12.3.9.              | Data Alignment                                               |            |

| 12.3.10.             | Programmable sampling time                                   |            |

| 12.3.11.             | Externally triggered conversion                              |            |

| 12.3.12.<br>12.3.13. | Configurable resolution                                      |            |

| 12.3.13.             | Dual-ADC mode                                                |            |

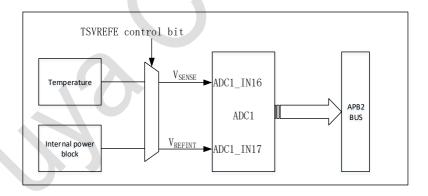

| 12.3.14.             | Temperature sensor and internal reference voltage            |            |

| 12.3.16.             | Battery monitoring                                           |            |

|                      | ,                                                            |            |

|                      | ADC interrupt                                                             |     |

|----------------------|---------------------------------------------------------------------------|-----|

| 12.4. A<br>12.4.1.   | DC RegisterStatus register (0x00: ADC_SR)                                 |     |

| 12.4.1.              | ADC Control Register 1 (0x04: ADC_CR1)                                    |     |

| 12.4.3.              | ADC Control Register 2 (0x08: ADC_CR2)                                    |     |

| 12.4.4.              | ADC Sampling Time Register 1 (0x0C: ADC_SMPR1)                            |     |

| 12.4.5.              | ADC Sampling Time Register 2 (0x10: ADC_SMPR2)                            |     |

| 12.4.6.              | ADC Injection Channel Data Offset Register x (0x14-0x20: ADC_JOFRx) x=1~4 |     |

| 12.4.7.              | ADC Watchdog High Threshold Register (0x24: ADC_HTR)                      |     |

| 12.4.8.              | ADC Watchdog Low Threshold Register (0x28: ADC_LTR)                       |     |

| 12.4.9.              | ADC Rule Sequence Register 1 (0x2C: ADC_SQR1)                             |     |

| 12.4.10.             | ADC Rule Sequence Register 2 (0x30: ADC_SQR2)                             |     |

| 12.4.11.             | ADC Rule Sequence Register 3 (0x34: ADC_SQR3)                             |     |

| 12.4.12.             | ADC Injection Sequence Register (0x38: ADC_JSQR)                          |     |

| 12.4.13.             | ADC Injection Data Register x (0x3C-0x48: ADC_JDRx) x=1~4                 |     |

| 12.4.14.             | ADC Rules Data Register (0x4C: ADC_DR)                                    |     |

| 12.4.15.             | ADC Calibration Configuration and Status Registers (0x50: ADC_CCSR)       |     |

| 12.4.16.             | ADC Register Map                                                          |     |

|                      | nced timers (TIM1 and TIM8)                                               |     |

|                      | ntroduction                                                               |     |

| 13.1.1.              | TIM1 and TIM8 main features                                               | 242 |

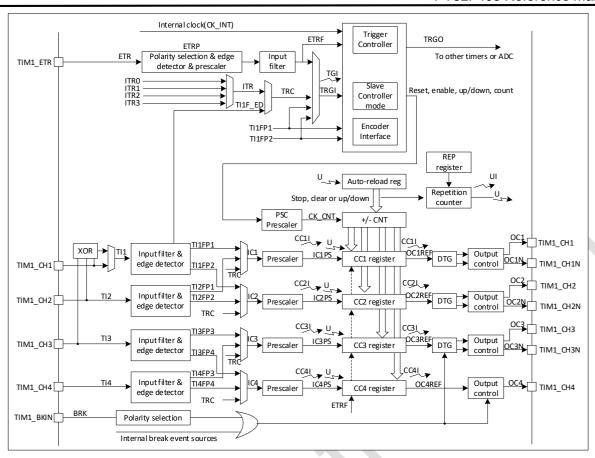

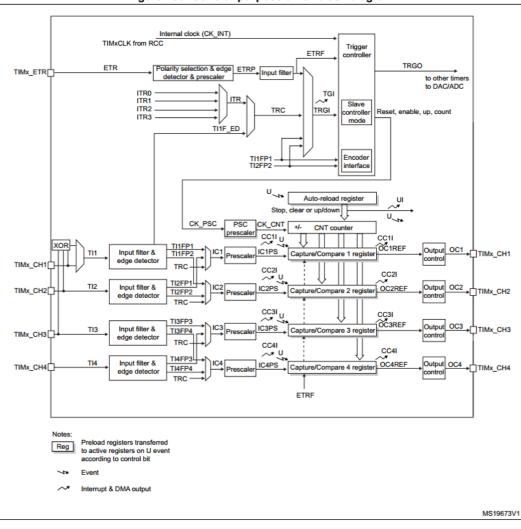

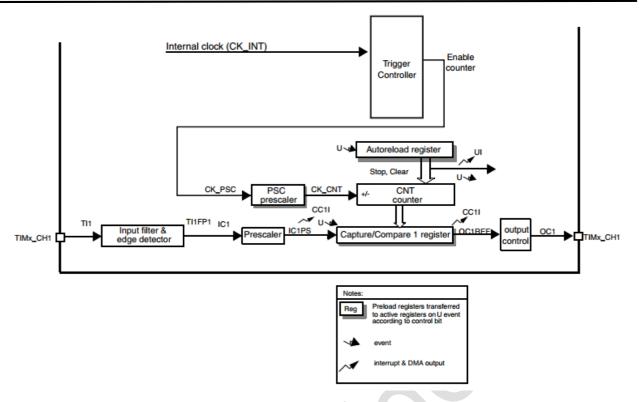

| 13.1.2.<br>13.2. T   | Module Block DiagramIM1 and TIM8 Functional Descriptions                  | 242 |

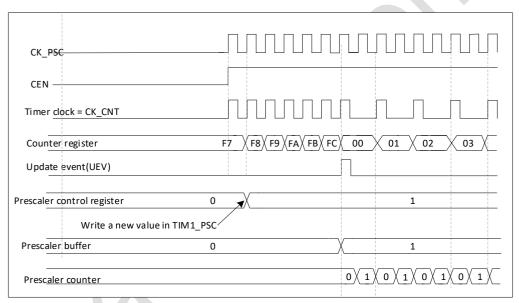

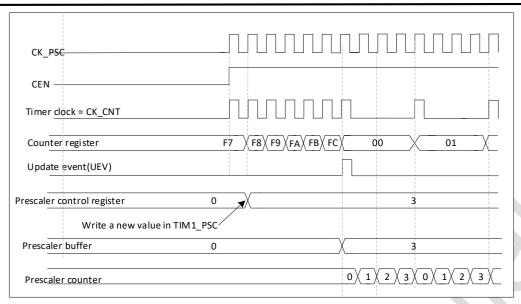

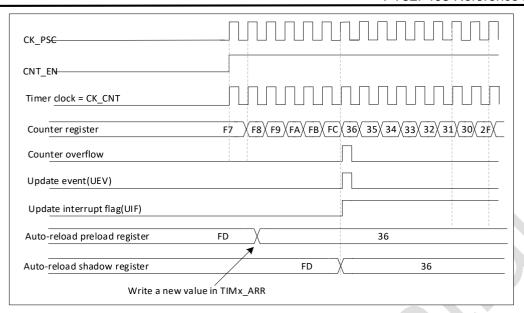

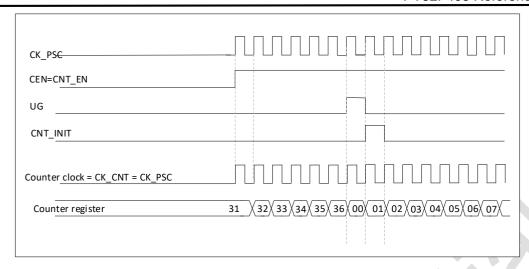

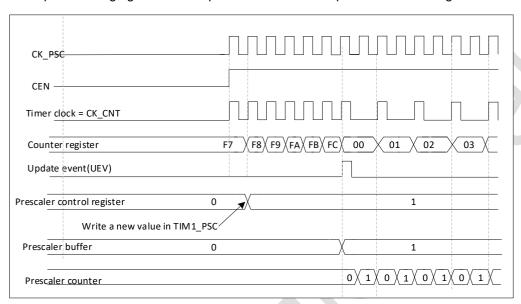

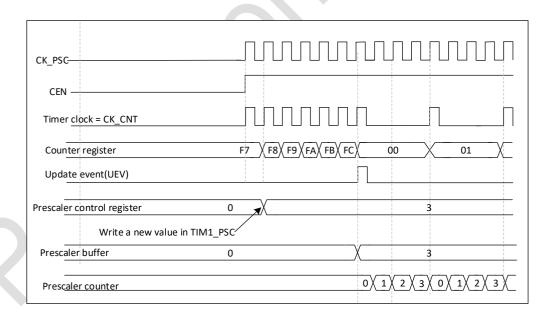

| 13.2.1.              | Time base unit                                                            |     |

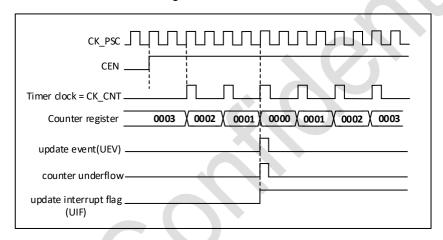

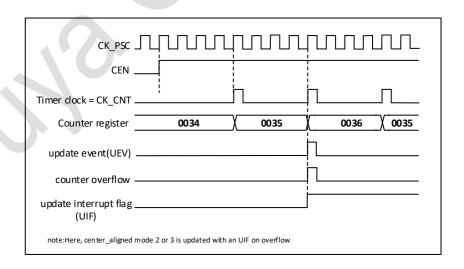

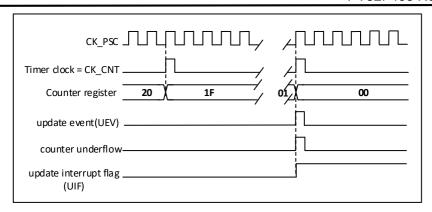

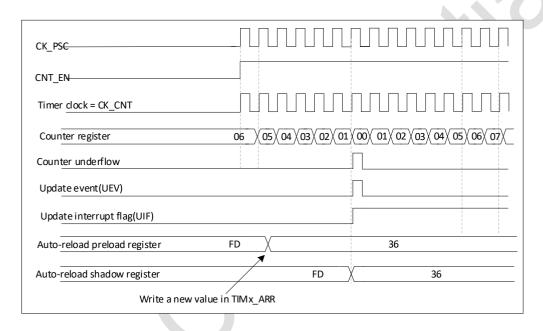

| 13.2.2.              | Counter mode                                                              |     |

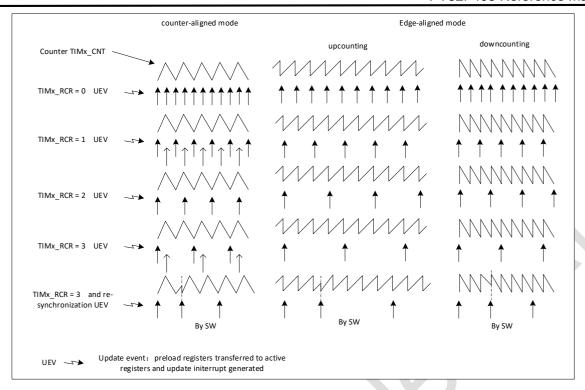

| 13.2.3.              | Repetition counter                                                        |     |

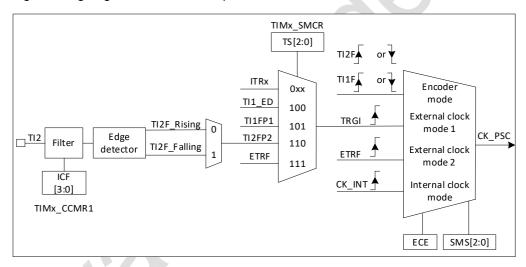

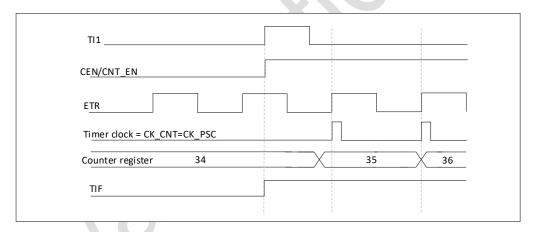

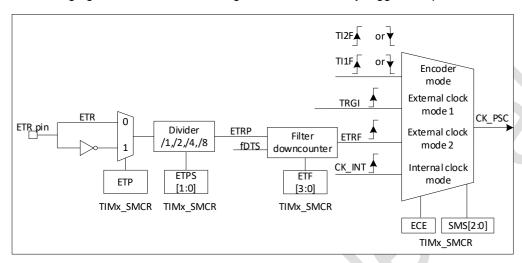

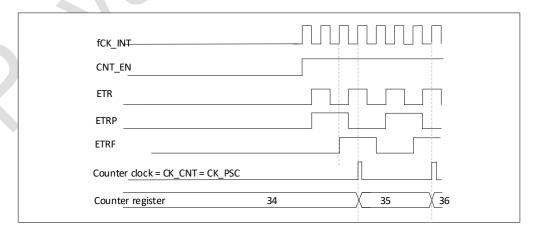

| 13.2.4.              | Clock selection                                                           |     |

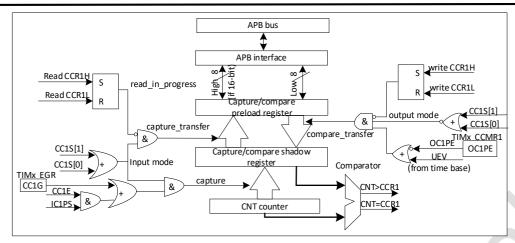

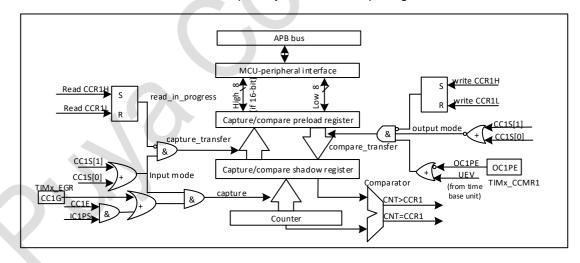

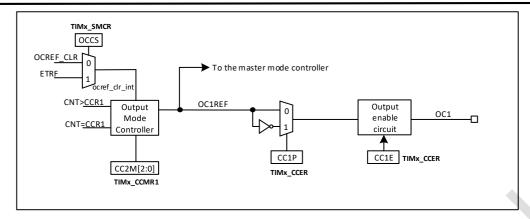

| 13.2.5.              | Capture/Compare Channel                                                   |     |

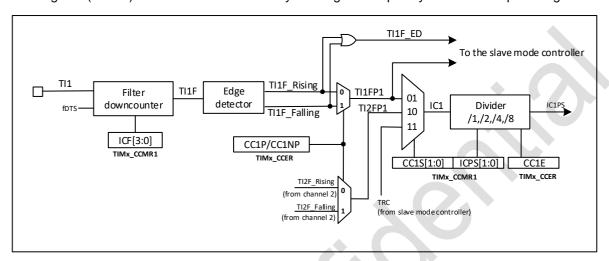

| 13.2.6.              | Input capture mode                                                        |     |

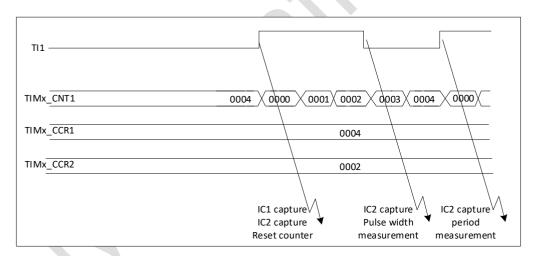

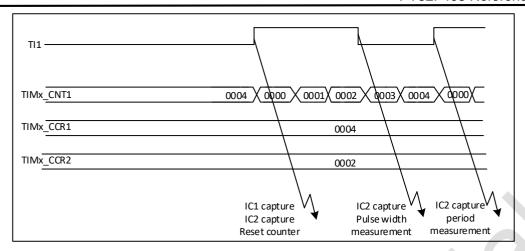

| 13.2.7.              | PWM Input Mode                                                            |     |

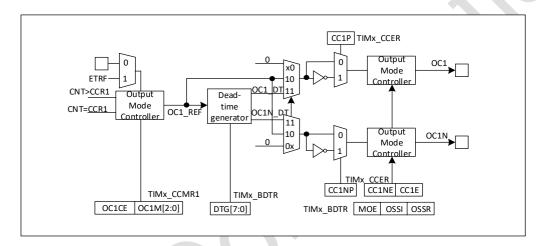

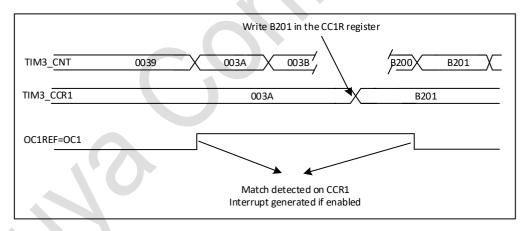

| 13.2.8.<br>13.2.9.   | Forced output mode  Output comparison mode                                |     |

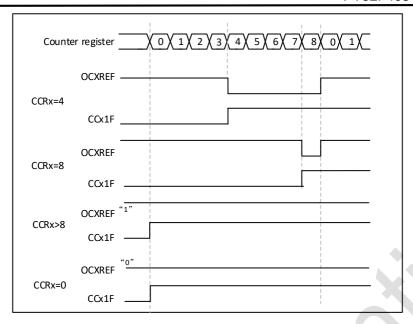

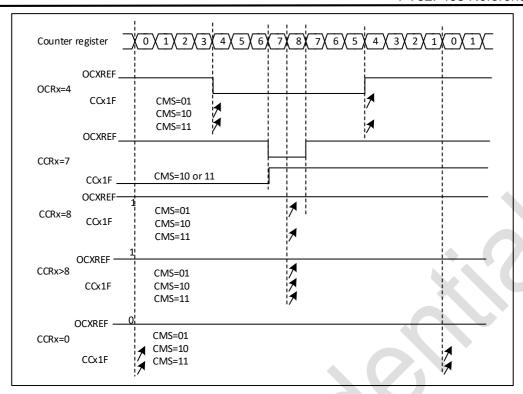

| 13.2.10.             | PWM Mode                                                                  |     |

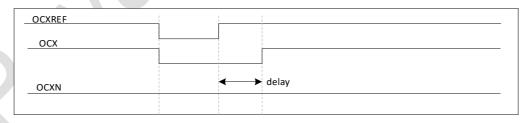

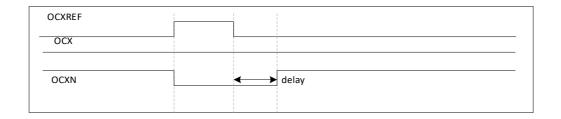

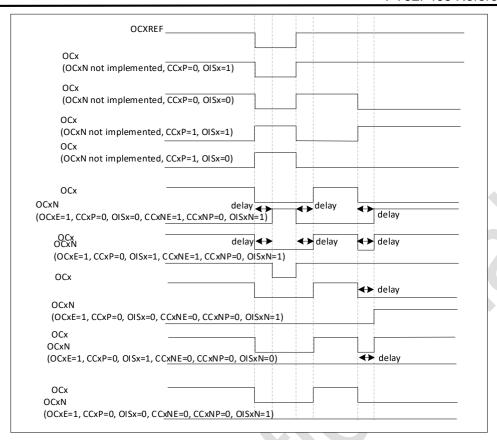

| 13.2.11.             | Complementary outputs and deadband insertion                              |     |

| 13.2.12.             | Use the brake function                                                    |     |

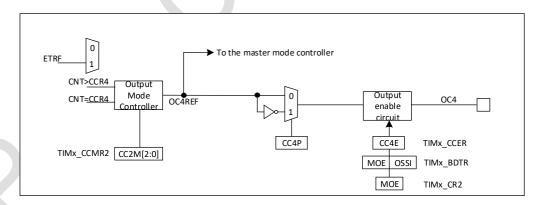

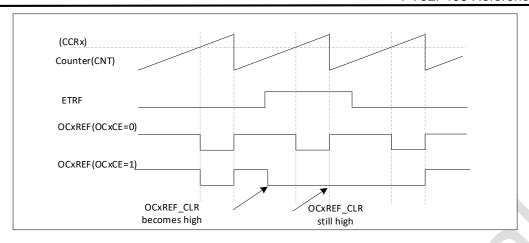

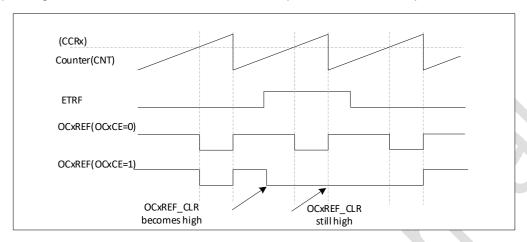

| 13.2.13.             | Clear the OCxREF signal on an external event                              |     |

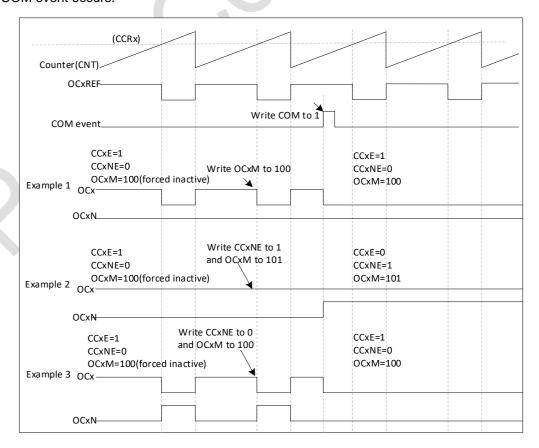

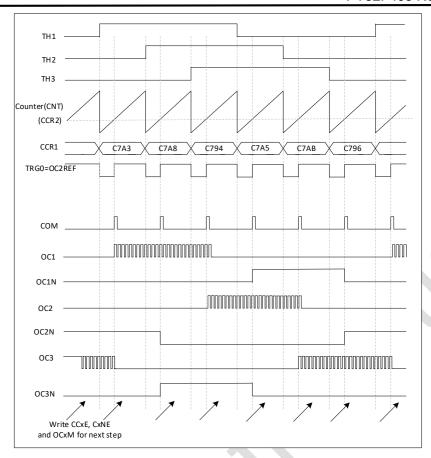

| 13.2.14.             | Generate six-step PWM outputs                                             | 269 |

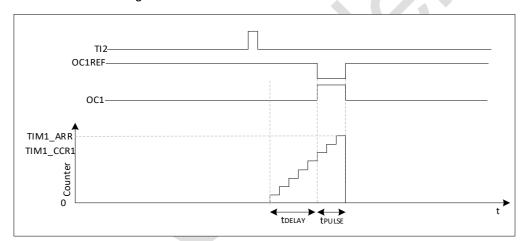

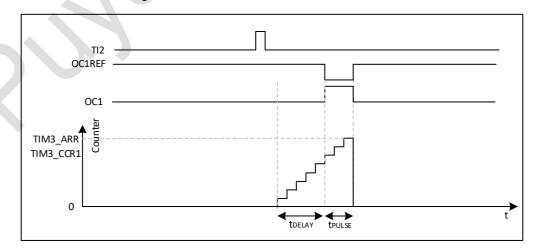

| 13.2.15.             | Single-pulse mode                                                         |     |

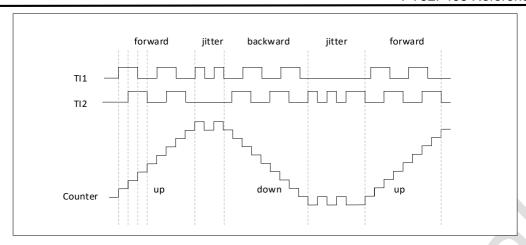

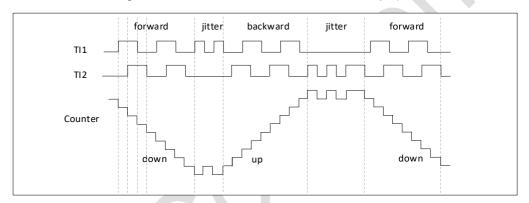

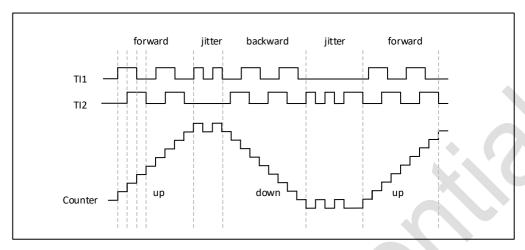

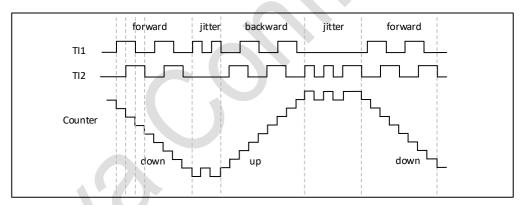

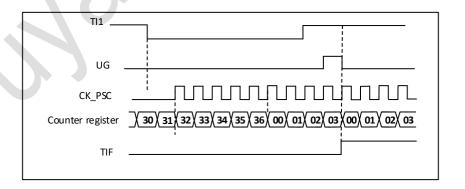

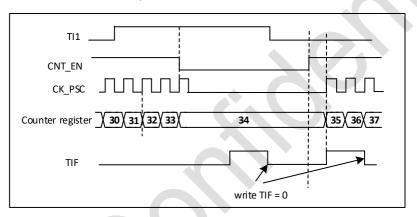

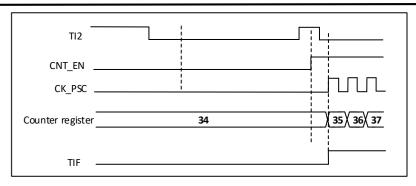

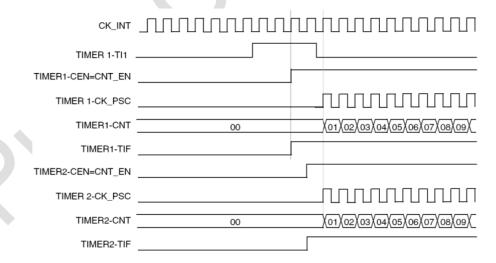

| 13.2.16.<br>13.2.17. | Encoder interface mode Timer Input Isochronous Function                   |     |

| 13.2.18.             | Interface with Hall sensors                                               |     |

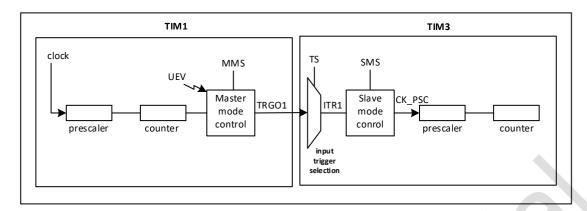

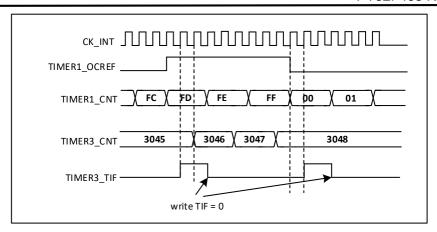

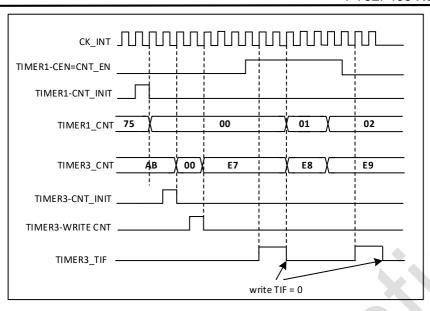

| 13.2.19.             | Synchronisation of TIMx timers and external triggers                      |     |

| 13.2.20.             | Timer Synchronisation                                                     |     |

| 13.2.21.             | Debug Mode                                                                |     |

|                      | egister Descriptions                                                      |     |

| 13.3.1.              | TIM1 and TIM8 control registers1 (TIMx_CR1)                               |     |

| 13.3.2.              | TIM1 and TIM8 control registers2 (TIMx_CR2)                               |     |

| 13.3.3.              | TIM1 and TIM8 Slave Mode Control Registers (TIMx_SMCR)                    |     |

| 13.3.4.              | TIM1 and TIM8 DMA/Interrupt Enable Registers (TIMx_DIER)                  |     |

| 13.3.5.              | TIM1 and TIM8 Status Registers (TIMx_SR)                                  |     |

| 13.3.6.              | TIM1 and TIM8 Event Generation Registers (TIMx_EGR)                       |     |

| 13.3.7.              | TIM1 and TIM8 Capture/Compare Mode Control Register 1 (TIMx_CCMR1)        |     |

| 13.3.8.              | TIM1 and TIM8 Capture/Compare Mode Registers2 (TIMx_CCMR2)                |     |

| 13.3.9.              | TIM1 and TIM8 Capture/Compare Enable Registers (TIMx_CCER)                |     |

| 13.3.10.             | TIM1 and TIM8 counters (TIMx_CNT)                                         |     |

| 13.3.11.             | TIM1 and TIM8 prescalers (TIMx_PSC)                                       |     |

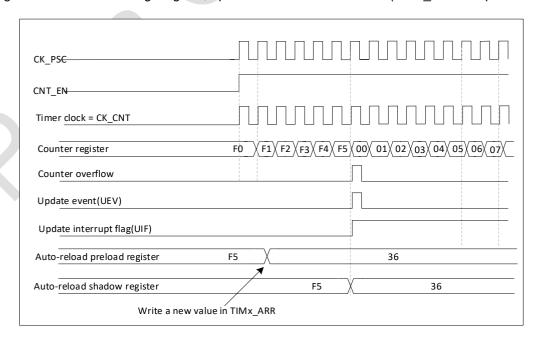

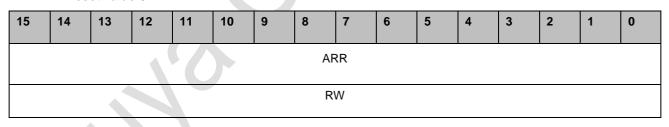

| 13.3.12.             | TIM1 and TIM8 Auto-Reload Registers (TIMx_ARR)                            |     |

| 13.3.13.             | TIM1 and TIM8 Repeat Counter Registers (TIMx_RCR)                         |     |

| 13.3.14.             | TIM1 and TIM8 Capture/Compare Register 1 (TIMx CCR1)                      | 303 |

| 13.3.15.             | TIM1 and TIM8 Capture/Compare Registers2 (TIMx_CCR2)                        | 304 |

|----------------------|-----------------------------------------------------------------------------|-----|

| 13.3.16.             | TIM1 and TIM8 Capture/Compare Registers3 (TIMx_CCR3)                        | 304 |

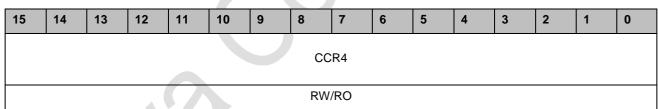

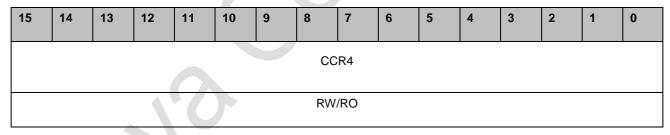

| 13.3.17.             | TIM1 and TIM8 Capture/Compare Registers4 (TIMx_CCR4)                        |     |

| 13.3.18.             | TIM1 and TIM8 Brake and Deadband Registers (TIMx_BDTR)                      |     |

| 13.3.19.             | TIM1 and TIM8 DMA Control Registers (TIMx_DCR)                              |     |

| 13.3.20.             | TIM1 and TIM8 Continuous Mode DMA Addresses (TIMx_DMAR)                     |     |

| 13.3.21.             |                                                                             |     |

|                      | al-purpose timers (TIM2 to TIM5)                                            |     |

| 14.1. Ir             | ntroduction                                                                 | 318 |

| 14.1.1.              | Main features of TIM 2/3/4/5                                                |     |

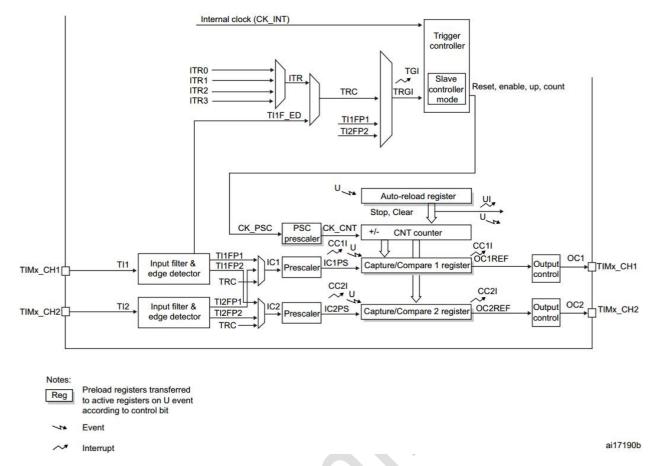

| 14.1.2.              | Module block diagram                                                        | 318 |

|                      | IM2/3/4/5 Functional Descriptions                                           |     |

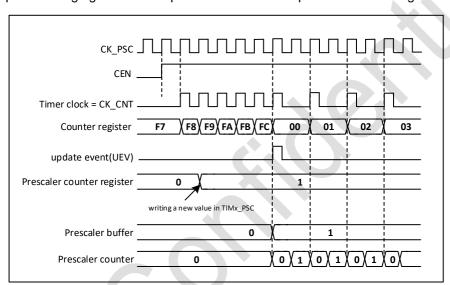

| 14.2.1.<br>14.2.2.   | Time base unit  Counter mode                                                |     |

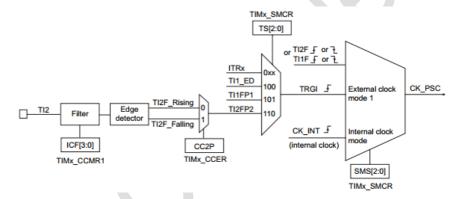

| 14.2.2.              | Clock selection                                                             |     |

| 14.2.4.              | Capture/Compare Channel                                                     |     |

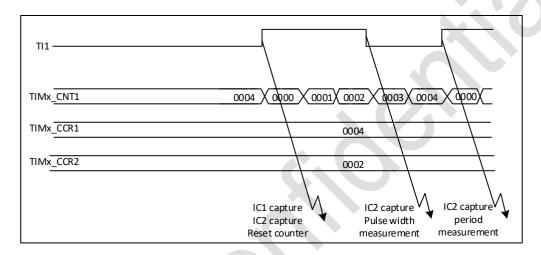

| 14.2.5.              | Input capture mode                                                          |     |

| 14.2.6.              | PWM Input Mode                                                              |     |

| 14.2.7.              | Forced output mode                                                          | 335 |

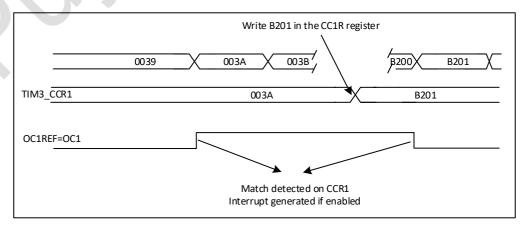

| 14.2.8.              | Output comparison mode                                                      |     |

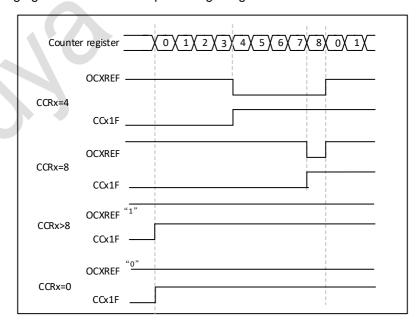

| 14.2.9.              | PWM mode                                                                    |     |

| 14.2.10.             | Clear the OCxREF signal on an external event                                |     |

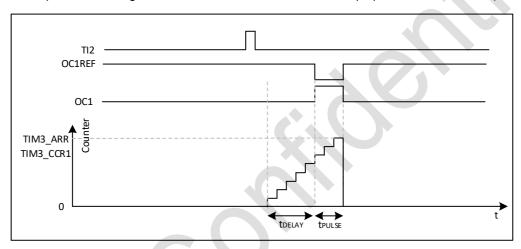

| 14.2.11.             | Single pulse mode                                                           |     |

| 14.2.12.             | Encoder interface mode                                                      |     |

| 14.2.13.             | Timer input heterodyne function                                             |     |

| 14.2.14.<br>14.2.15. | Synchronisation of TIMx timers and external triggers  Timer Synchronisation | 344 |

| 14.2.16.             | Debug Mode                                                                  | 352 |

|                      | egister Description                                                         | 352 |

| 14.3.1.              | TIM2/3/4/5 control register 1(TIMx_CR1)                                     |     |

| 14.3.2.              | TIM2/3/4/5 control registers2 (TIMx_CR2)                                    |     |

| 14.3.3.              | TIM2/3/4/5 slave mode control registers (TIMx_SMCR)                         |     |

| 14.3.4.              | TIM2/3/4/5 DMA/Interrupt Enable Registers (TIMx_DIER)                       |     |

| 14.3.4.              | TIM2/3/4/5 status registers (TIMx_SR)                                       |     |

|                      | TIM2/3/4/5 event generation registers (TIMx_EGR)                            |     |

| 14.3.6.              |                                                                             |     |

| 14.3.7.              | TIM2/3/4/5 Capture/comparison mode control register 1 (TIMx_CCMR1)          |     |

| 14.3.8.              | TIM2/3/4/5 Capture/Compare Mode Register 2 (TIMx_CCMR2)                     | 366 |

| 14.3.9.              | TIM2/3/4/5 Capture/Compare Enable Registers (TIMx_CCER)                     |     |

| 14.3.10.             | TIM2/3/4/5 counters (TIMx_CNT)                                              |     |

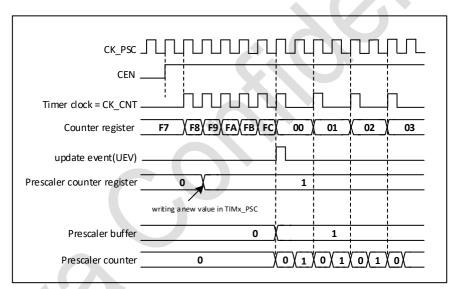

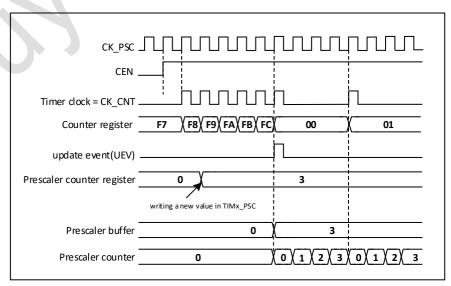

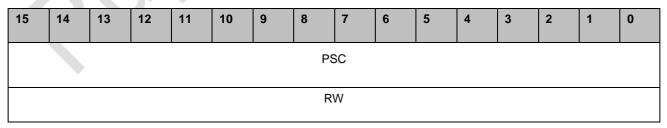

| 14.3.11.             | TIM2/3/4/5 prescalers (TIMx_PSC)                                            |     |

| 14.3.12.             | TIM2/3/4/5 Automatic Reload Registers (TIMx_ARR)                            |     |

| 14.3.13.             | TIM2/3/4/5 Capture/comparison register 1 (TIMx_CCR1)                        |     |

| 14.3.14.             | TIM2/3/4/5 Capture/comparison register 2 (TIMx_CCR2)                        |     |

| 14.3.15.             | TIM2/3/4/5 Capture/comparison registers3 (TIMx_CCR3)                        |     |

| 14.3.16.             | TIM2/3/4/5 Capture/comparison registers4 (TIMx_CCR4)                        |     |

| 14.3.17.             | TIM2/3/4/5 DMA Control Registers (TIMx_DCR)                                 |     |

| 14.3.18.             | DMA address for TIM2/3/4/5 continuous mode (TIMx_DMAR)                      |     |

| 14.3.19.             | TIM2/3/4/5 register mapping                                                 | 374 |

|                      | al-purpose timer (TIM9 and TIM12)                                           |     |

|                      | ntroduction                                                                 |     |

| 15.1.1.              | TIM9 and TIM12 main features                                                |     |

| 15.1.2.              | Module Block DiagramIM9 and TIM12 Functional Descriptions                   |     |

| 15.2. T<br>15.2.1.   | Time base unit                                                              |     |

| 15.2.1.              | Counter modes                                                               |     |

| 15.2.2.              | Clock selection                                                             |     |

| 15.2.4.              | Capture/compare channels                                                    |     |

| 15.2.5.              | Input capture mode                                                          |     |

| 15.2.6.              | PWM input mode                                                              |     |

|                      | Force output mode                                                           |     |

| 15.2.8.            | Output compare mode                                                 |     |

|--------------------|---------------------------------------------------------------------|-----|

| 15.2.9.            | PWM mode                                                            |     |

| 15.2.10            |                                                                     |     |

| 15.2.11            | ,                                                                   |     |

| 15.2.12            | ·                                                                   |     |

| 15.2.13            | <b>5</b>                                                            |     |

|                    | Register Description                                                |     |

| 15.3.1.            | TIM9 and TIM12 control register 1 (TIMx_CR1)                        |     |

| 15.3.2.            | TIM9 and TIM12 Slave Mode Control Register (TIMx_SMCR)              |     |

| 15.3.3.            | TIM9 and TIM12 interrupt enable register (TIMx_DIER)                |     |

| 15.3.4.            | TIM9 and TIM12 status register (TIMx_SR)                            |     |

| 15.3.5.            | TIM9 and TIM12 event generation register (TIMx_EGR)                 |     |

| 15.3.6.            | TIM9 and TIM12 Capture/Compare Mode Control Register 1 (TIMx_CCMR1) |     |

| 15.3.7.            | TIM9 and TIM12 Capture/Compare Enable Registers (TIMx_CCER)         | 411 |

| 15.3.8.            | TIM9 and TIM12 Counters (TIMx_CNT)                                  | 413 |

| 15.3.9.            | TIM9 and TIM12 Prescaler (TIMx_PSC)                                 | 413 |

| 15.3.10            |                                                                     |     |

| 15.3.11            |                                                                     |     |

| 15.3.12            |                                                                     |     |

| 15.3.13            | TIM9 and TIM12 register map                                         | 415 |

|                    | eral-purpose timer(TIM10/TIM11/TIM13/TIM14)                         |     |

|                    | ntroduction                                                         |     |

| 16.1.1.            |                                                                     |     |

| 16.2. <sup>-</sup> | FIMx functional description                                         | 421 |

| 16.2.1.            | Time-base unit                                                      | 421 |

| 16.2.2.            | Counter Mode                                                        | 422 |

| 16.2.3.            | Clock Selection                                                     |     |

| 16.2.4.            | Capture/compare channels                                            |     |

| 16.2.5.            | Input capture mode                                                  | 426 |

| 16.2.6.            | Forced output mode                                                  |     |

| 16.2.7.            | Output compare mode                                                 | 427 |

| 16.2.8.            | PWM mode                                                            |     |

| 16.2.9.            | Single pulse mode                                                   | 430 |

| 16.2.10            |                                                                     |     |

| 16.2.11            | J                                                                   |     |

|                    | Register Description                                                |     |

| 16.3.1.            |                                                                     | 431 |

| 16.3.2.            | TIMx interrupt enable register (TIMx_DIER)                          |     |

| 16.3.3.            | TIMx Status Register (TIMx_SR)                                      | 432 |

| 16.3.4.            | TIMx Event Generation Register (TIMx_EGR)                           |     |

| 16.3.5.            | TIMx Capture/Compare Mode Control Register 1 (TIMx_CCMR1)           |     |

| 16.3.6.            | TIMx Capture/Compare Enable Register (TIMx_CCER)                    |     |

| 16.3.7.<br>16.3.8. | TIMx counter (TIMx_CNT)TIMx Prescaler (TIMx_PSC)                    |     |

| 16.3.9.            |                                                                     |     |

| 16.3.10            |                                                                     | 430 |

| 16.3.10            | TIMx option register (TIMx_OR)                                      | 433 |

| 16.3.11            |                                                                     |     |

|                    | eral-purpose timers (TIM 6 and TIM17)                               |     |

|                    | ntroduction                                                         |     |

| 17.1.1.            | TIM6 and TIM7 main features                                         |     |

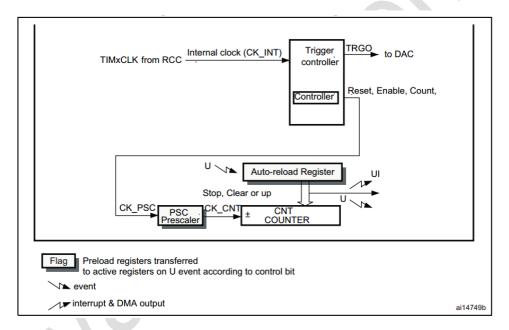

| 17.1.2.            | Module Block Diagram                                                |     |

|                    | FIM6 and TIM7 Functional Descriptions                               |     |

| 17.2.1.            | Time-base unit                                                      |     |

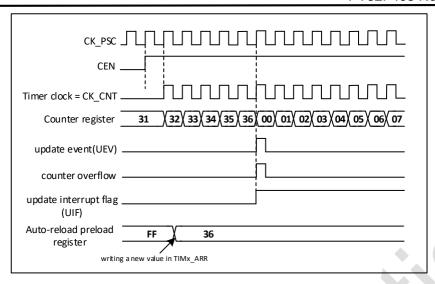

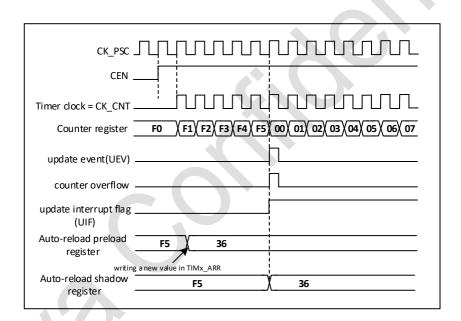

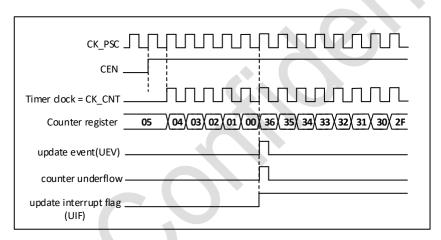

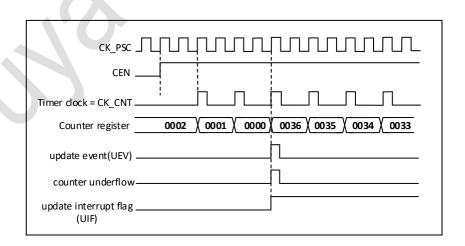

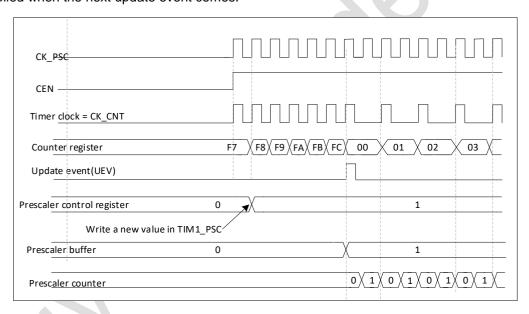

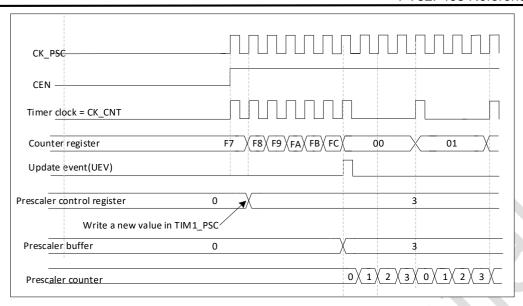

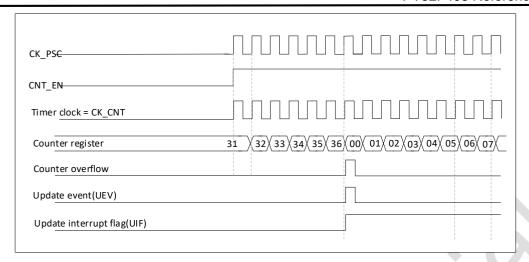

| 17.2.2.            | Counter operation                                                   |     |

| 17.2.3.            | Debug mode                                                          |     |

|                    | Register Description                                                |     |

| 17.3.1.            | TIM6 and TIM7 control register 1 (TIMx_CR1)                         |     |

| 17.3.2.            | TIM6 and TIM7 control register 2 (TIMx_CR2)                         |     |

| 17.3.3.            | TIM6 and TIM7 DMA/interrupt enable registers (TIMx_DIER)            | 451 |

| 17.3.4.            | TIM6 and TIM7 status registers (TIMx_SR)                            |     |

| 17.3.5.            |                                                                     |     |

| 17.3.6   | . TIM6 and TIM7 Counters (TIMx_CNT)                  | 452 |

|----------|------------------------------------------------------|-----|

| 17.3.7   | . TIM6 and TIM7 Prescaler (TIMx_PSC)                 | 453 |

| 17.3.8   |                                                      |     |

| 17.3.9   | . TIM6 and TIM7 register maps                        | 453 |

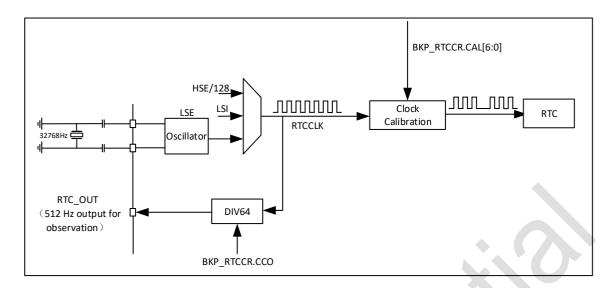

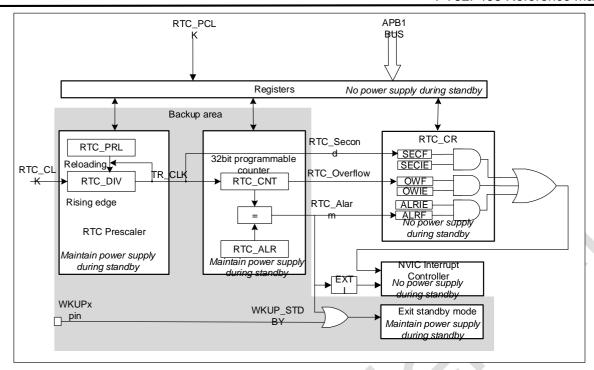

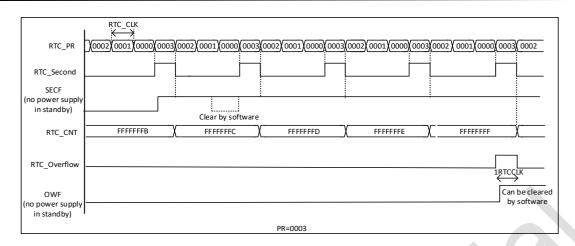

| 18. Rea  | I time clock (RTC)                                   | 457 |

| 18.1.    | Introduction                                         | 457 |

| 18.1.1   | . Main features                                      | 457 |

| 18.1.2   | . Module Block Diagram                               | 457 |

| 18.2.    | Function Description                                 | 458 |

| 18.2.1   | . Register Reset                                     | 458 |

| 18.2.2   | . Read RTC register                                  | 459 |

| 18.2.3   | . Configure RTC register                             | 459 |

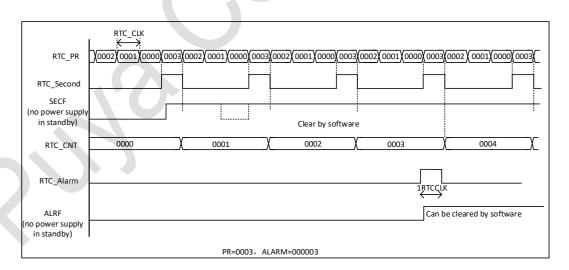

| 18.2.4   | . RTC flag setting                                   | 460 |

| 18.2.5   | . RTC Timing                                         | 460 |

| 18.3.    | Register description (base address 0x4000_2800)      | 461 |

| 18.3.1   | . RTC Control Register High (RTC_CRH) (0x00)         | 461 |

| 18.3.2   |                                                      |     |

| 18.3.3   | . RTC Prescaler Load Register High (RTC_PRLH) (0x08) |     |

| 18.3.4   | . RTC Prescaler Load Register Low (RTC_PRLL) (0x0C)  | 464 |

| 18.3.5   |                                                      | 465 |

| 18.3.6   |                                                      |     |

| 18.3.7   | • • • • • • • • • • • • • • • • • • • •              | 466 |

| 18.3.8   |                                                      | 466 |

| 18.3.9   |                                                      |     |

| 18.3.1   |                                                      |     |

| 18.3.1   |                                                      |     |

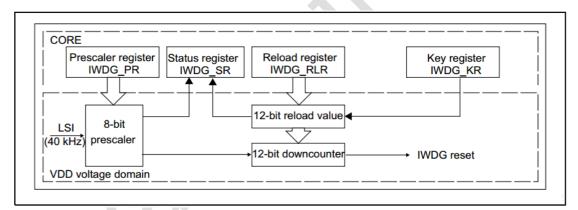

| 19. Inde | ependent watchdog (lWDG)                             | 470 |

| 19.1.    | Introduction                                         |     |

| 19.2.    | Main features                                        |     |

| 19.3.    | Function Description                                 |     |

| 19.3.1   | ·                                                    |     |

| 19.3.2   |                                                      |     |

| 19.3.3   |                                                      | 471 |

| 19.3.4   |                                                      |     |

| 19.3.5   |                                                      |     |

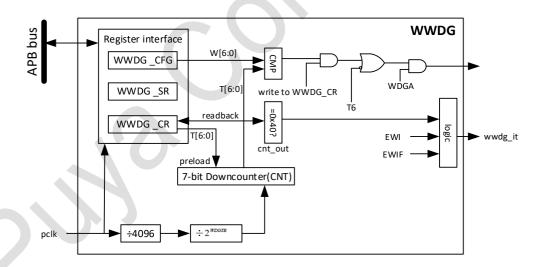

|          | tem window watchdog (WWDG)                           |     |

| 20.1.    | Introduction                                         |     |

| 20.1.1   |                                                      |     |

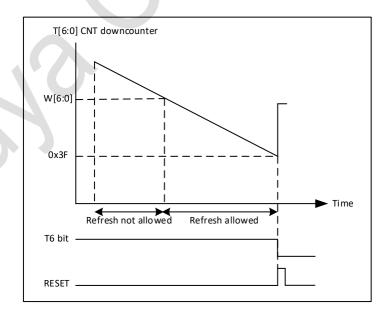

| 20.2.    | WWDG Function Description                            |     |

| 20.3.    | How to write a watchdog timeout program              |     |

| 20.4.    | Debug mode                                           |     |

| 20.5.    | Register Description                                 |     |

| 20.5.1   |                                                      |     |

| 20.5.2   | <b>5</b>                                             |     |

| 20.5.3   |                                                      |     |

| 20.5.4   | • · · · · · · · · · · · · · · · · · · ·              |     |

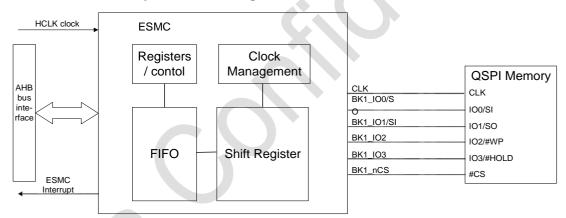

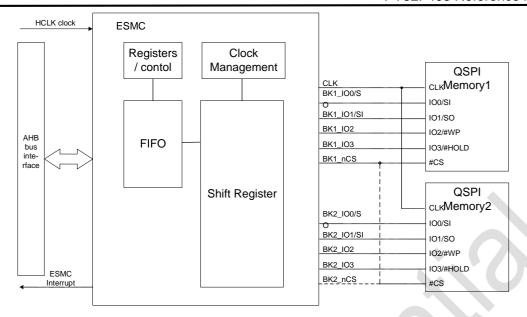

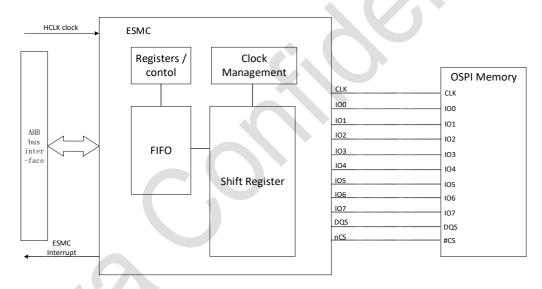

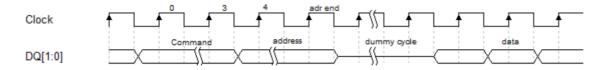

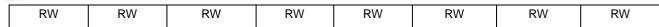

|          | ernal Serial Memory Controller (ESMC)                | 481 |

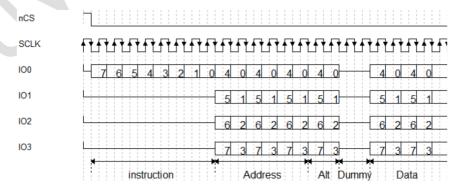

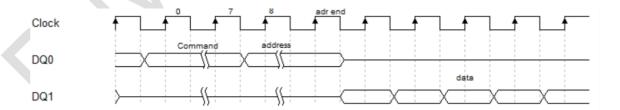

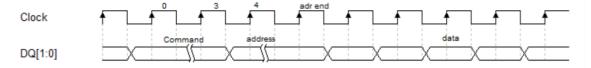

| 21.1.    | Introduction                                         |     |

| 21.2.    | Main features                                        |     |

| 21.3.    | Function Description                                 |     |

| 21.3.1   | ·                                                    |     |

|          | ESMC Functional Description                          |     |

| 21.3.3   |                                                      |     |

| 21.3.4   | , , ,                                                |     |

| 21.3.5   | , , ,                                                |     |

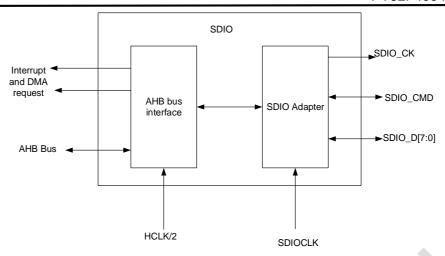

|          | O Interface (SDIO)                                   |     |

| 22.1.    | Introduction                                         |     |

| 22.1.1   |                                                      |     |

| 22.1.1   |                                                      |     |

| 22.1.2   | Function Description                                 |     |

| 22.2.1   | •                                                    |     |

| 22.2.1   | ·                                                    |     |

|          | Card Function Description                            |     |

| 22.2.0   |                                                      |     |

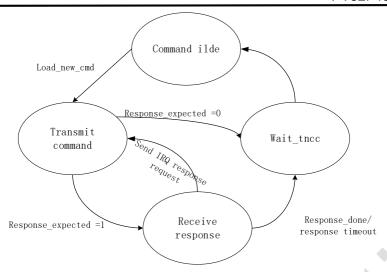

| 22.2.4. Command                                        | 526 |

|--------------------------------------------------------|-----|

| 22.2.5. Response                                       |     |

| 22.3. Software Application Notes                       |     |

| 22.3.1. Power Control                                  |     |

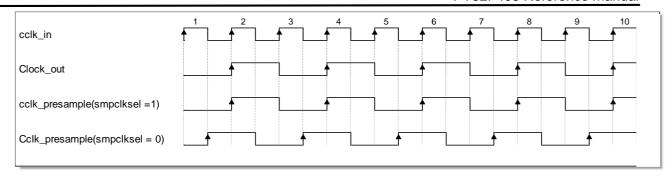

| 22.3.2. Clock program                                  |     |

| 22.3.3. Initialization                                 |     |

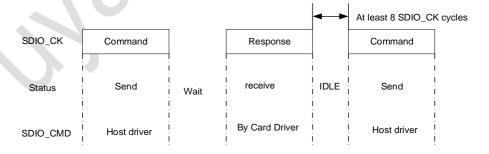

| 22.3.4. No data command and no response sequence       |     |

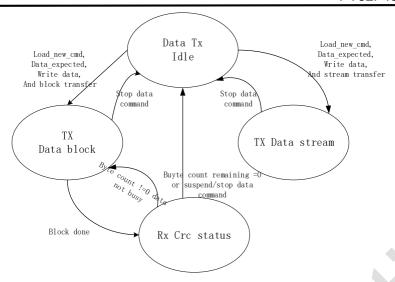

| 22.3.5. Data transfer command                          |     |

| 22.3.6. Single or multi-block writing                  |     |

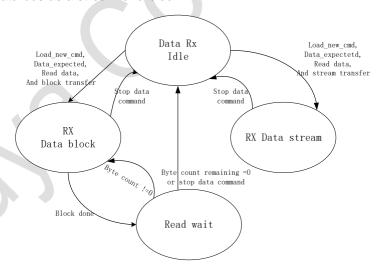

| 22.3.7. Data stream reading                            |     |

| 22.3.8. Data stream writing                            |     |

| 22.3.9. Send stop and interrupt during transmission    |     |

| 22.3.10. Suspend or resume sequence                    |     |

| 22.3.11. Read Wait Sequence                            |     |

| 22.3.12. Controller/DMA/FIFO Reset Usage               |     |

| 22.3.13. Dedicated interrupt                           |     |

| 22.3.14. Asynchronous interrupt                        |     |

| 22.3.15. Error Handling                                |     |

| 22.3.16. CT_ATA Operation                              |     |

| 22.4. Register Configuration                           |     |

| 22.4.1. SDIO power control register (SDIO_POWER)       | 547 |

| 22.4.2. SDIO clock control register (SDIO_CLKCR)       | 547 |

| 22.4.3. SDIO parameter register (SDIO_ARG)             |     |

| 22.4.4. SDIO command register (SDIO_CMD)               |     |

| 22.4.5. SDIO command response register (SDIO_RESPCMD)  |     |

| 22.4.6. SDIO command response 14 register (SDIO_RESPX) |     |

| 22.4.7. SDIO data timer register (SDIO_TMOUT)          |     |

| 22.4.8. SDIO data block length register (SDIO_BLKSIZE) |     |

| 22.4.9. SDIO Data Length Register (SDIO_DLEN)          |     |

| 22.4.10. SDIO control register (SDIO_CTRL)             |     |

| 22.4.11. SDIO Status Register (SDIO_STA)               |     |

| 22.4.12. SDIO interrupt status register (SDIO_INTSTS)  |     |

| 22.4.13. SDIO interrupt mask register (SDIO_INTMASK)   |     |

| 22.4.14. SDIO FIFO threshold register (SDIO_FIFOTH)    |     |

| 22.4.15. SDIO send to card counter (SDIO_TCBCNT)       |     |

| 22.4.16. SDIO send to FIFO counter (SDIO_TBBCNT)       |     |

| 22.4.17. SDIO data FIFO register (SDIO_FIFODATA)       |     |

| 22.4.18. SDIO register map                             |     |

| 23. USB Full Speed Device Interface (USB)              |     |

| 23.1. Introduction                                     |     |

| 23.2. Main features                                    |     |

| 23.3. Function Description                             |     |

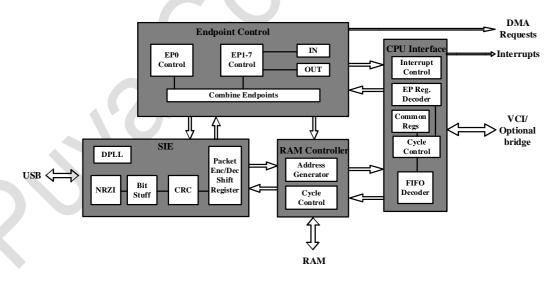

| 23.3.1. Module Block Diagram                           |     |

| 23.3.2. Function Description                           |     |

| 23.3.4. USB Register Description                       |     |

| 23.3.4. CAN bus controller                             |     |

| 24.1. Introduction                                     |     |

| 24.2. Main features                                    |     |

| 24.3. Function Description                             |     |

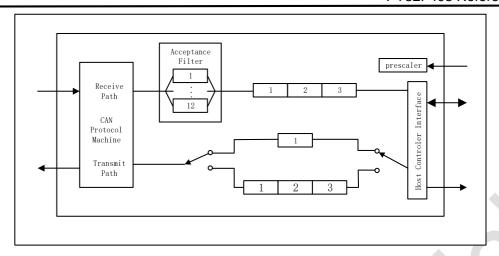

| 24.3.1. Module Block Diagram                           |     |

| 24.3.2. Action Mode                                    |     |

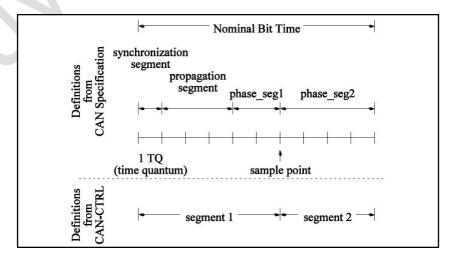

| 24.3.3. Baud rate setting                              |     |

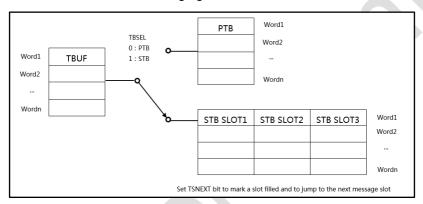

| 24.3.4. Send buffer                                    |     |

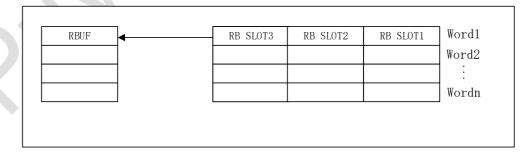

| 24.3.5. Receiving buffer                               |     |

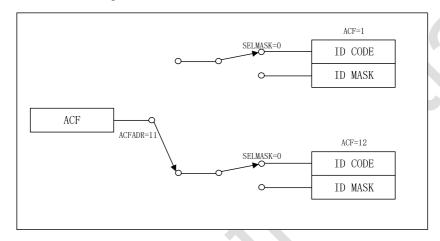

| 24.3.6. Receive filter register set                    |     |

| 24.3.7. Data transmission                              |     |

| 24.3.8. Single data transmission                       |     |

| 24.3.9. Cancel data sending                            |     |

| 24.3.10. Data reception                                |     |

| 24.3.11. Error Handling                                |     |

| 24.3.12. Node closure                                  |     |

| 24.3.13. Arbitration Failure Location Capture          |     |

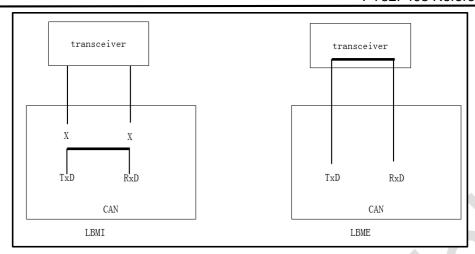

| 24.3.14. | Loopback mode                                            | . 602 |

|----------|----------------------------------------------------------|-------|

| 24.3.15. | Silent mode                                              | . 603 |

| 24.3.16. | Software reset function                                  | . 603 |

| 24.3.17. | Compatible with CAN-FD function                          | . 605 |

| 24.3.18. | Time-triggered TTCAN                                     | . 605 |

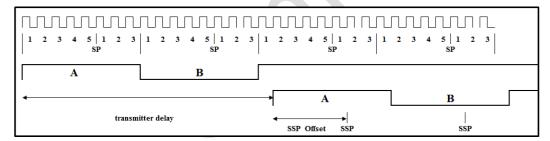

| 24.3.19. | TDC or RDC                                               |       |

| 24.3.20. | Interruption                                             |       |

| 24.4. R  | egister Description                                      | . 608 |

| 24.4.1.  | Node Configuration Register (CANFD_TSNCR)                |       |

| 24.4.2.  | Bit Timing Configuration Register (CANFD_ACBTR)          | . 608 |

| 24.4.3.  | CANFD_FDBTR                                              |       |

| 24.4.4.  | Limit and Prescaler Configuration Register (CANFD_RLSSP) |       |

| 24.4.5.  | Status Register (CANFD_IFR)                              | . 611 |

| 24.4.6.  | Interrupt Enable Register (CANFD_IER)                    | 613   |

| 24.4.7.  | Transmission Status Register (CANFD_TSR)                 |       |

| 24.4.8.  | Global Configuration Register (CANFD_MCR)                |       |

| 24.4.9.  | Error Warning Register (CANFD_WECR)                      |       |

| 24.4.10. | Reference ID register (CANFD_REFMSG)                     |       |

| 24.4.11. | TTCAN Configuration Register (CANFD_TTCR)                |       |

| 24.4.12. | TTCAN Trigger Register (CANFD_TTTR)                      | 624   |

| 24.4.13. | CANFD_SCMS                                               |       |

| 24.4.13. | Filter Group Control Register (CANFD_ACFCR)              |       |

| 24.4.14. | Filter group code register (CANFD_ACFC)                  |       |

|          | Filter groupmask register (CANFD_ACFC)                   |       |

| 24.4.16. | CAN Descrive BUE register (CANED, BRUE)                  | . 020 |

| 24.4.17. | CAN Receive BUF register (CANFD_RBUF)                    |       |

| 24.4.18. | CAN transmit BUF register (CANFD_TBUF)                   |       |

| 24.4.19. | CAN register map                                         |       |

|          | Peripheral Interface (SPI)                               |       |

|          | ntroduction                                              |       |

| 25.1.1.  | Main features                                            |       |

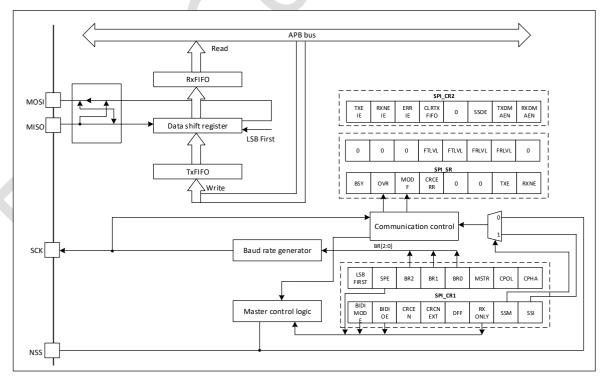

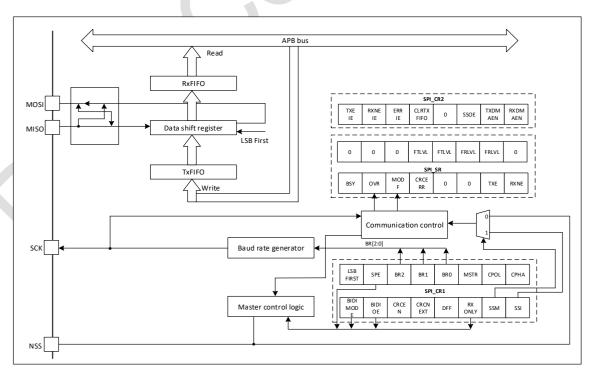

| 25.1.2.  | Module Block Diagram                                     |       |

|          | PI Function Description                                  | . 631 |

| 25.2.1.  | Overview                                                 |       |

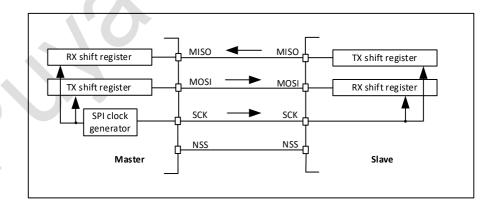

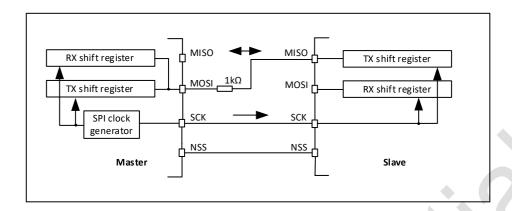

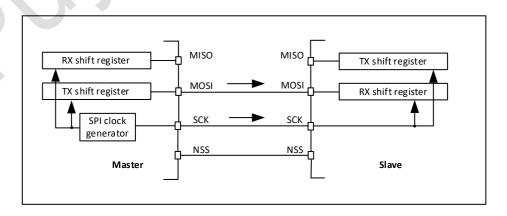

| 25.2.2.  | Single-master and single-slave communication             |       |

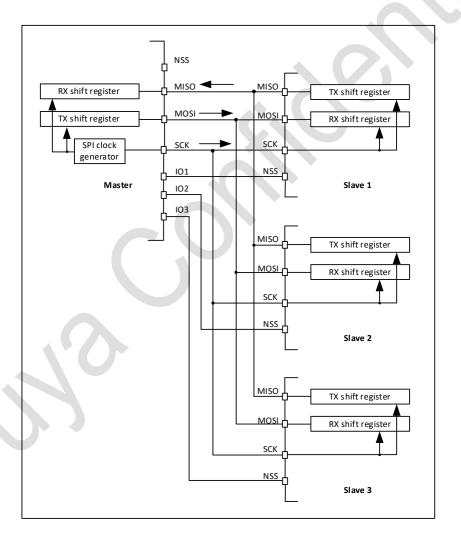

| 25.2.3.  | Multi-slave communication                                |       |

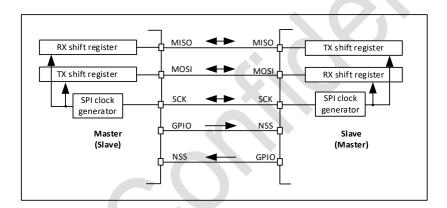

| 25.2.4.  | Multi-host communication                                 |       |

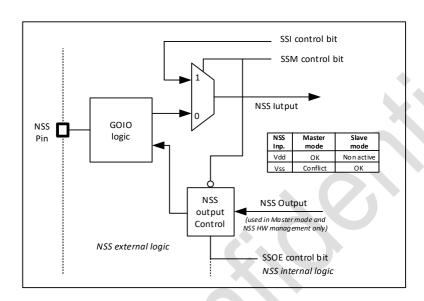

| 25.2.5.  | From Selection (NSS) Pin Management                      |       |

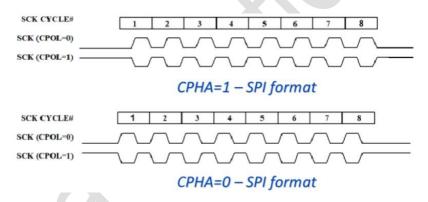

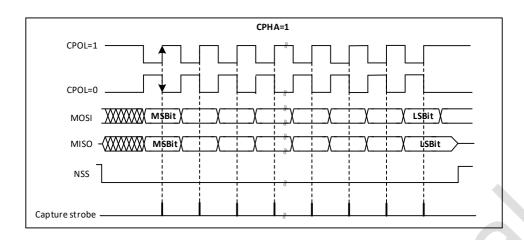

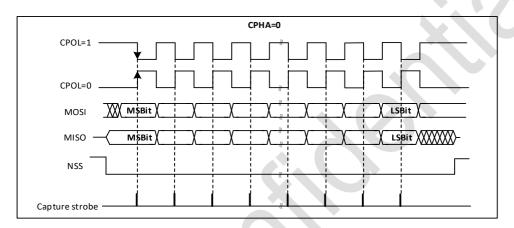

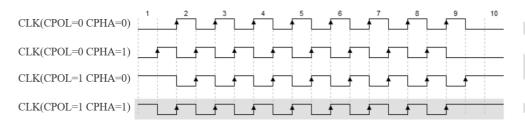

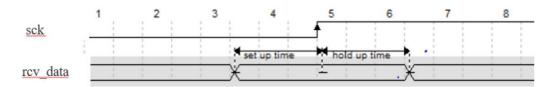

| 25.2.6.  | Communication Format                                     | . 636 |

| 25.2.7.  | SPI Configuration                                        |       |

| 25.2.8.  | SPI Enable Flow                                          |       |

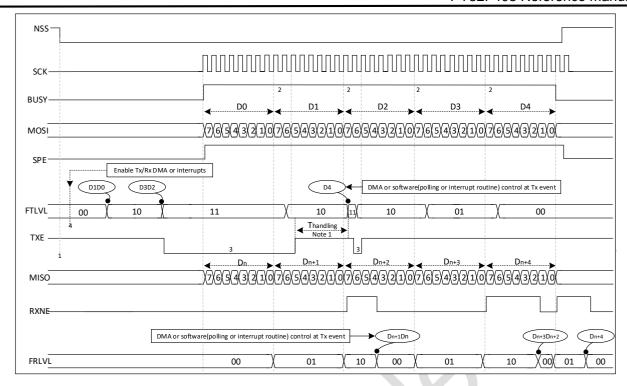

| 25.2.9.  | Data transmission and reception process                  |       |

| 25.2.10. | Status Flag                                              |       |

| 25.2.11. | Error flags                                              | . 643 |

| 25.2.12. | SPI Interrupt                                            |       |

| 25.2.13. | CRC Calculation                                          | . 644 |

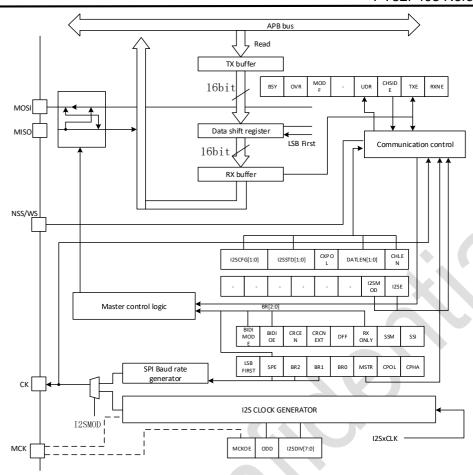

| 25.3. I2 | 2S Function Description                                  | . 645 |

| 25.3.1.  | Introduction                                             | . 645 |

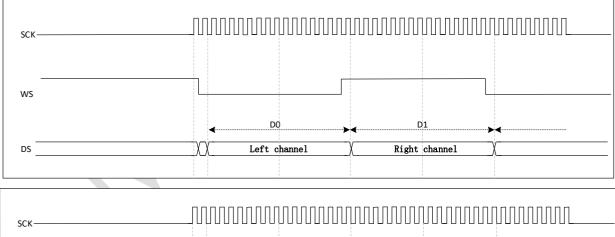

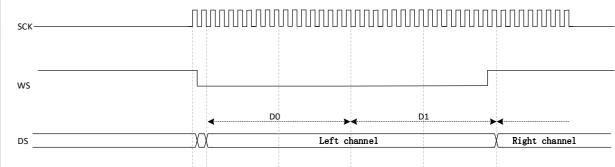

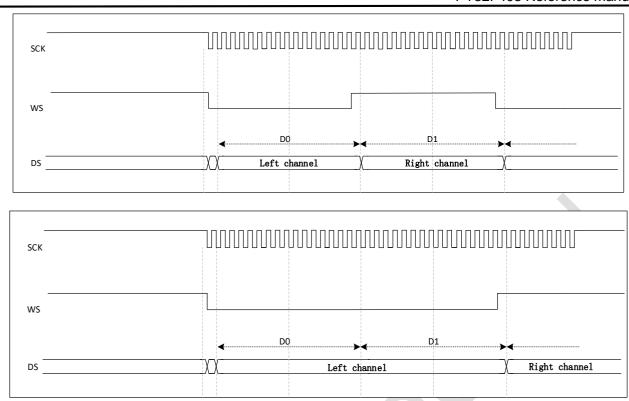

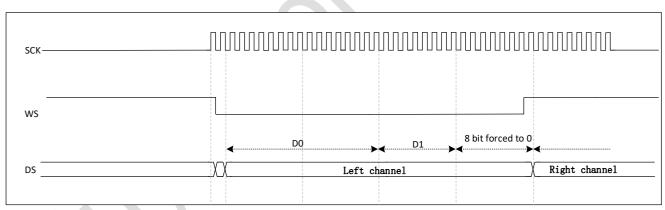

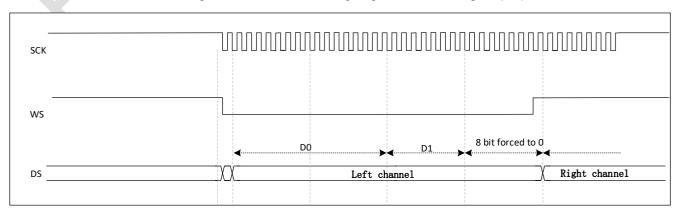

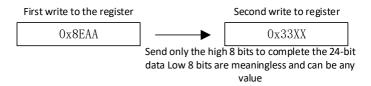

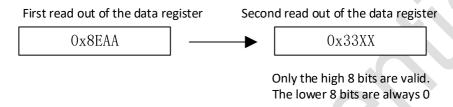

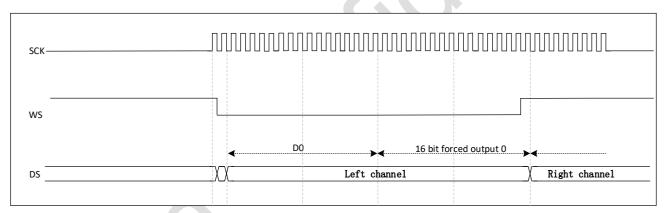

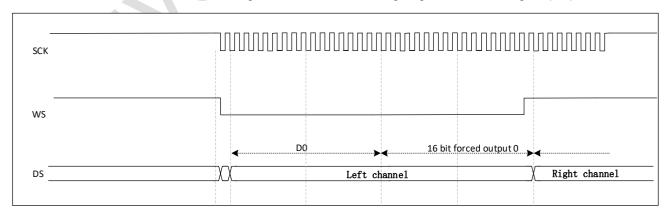

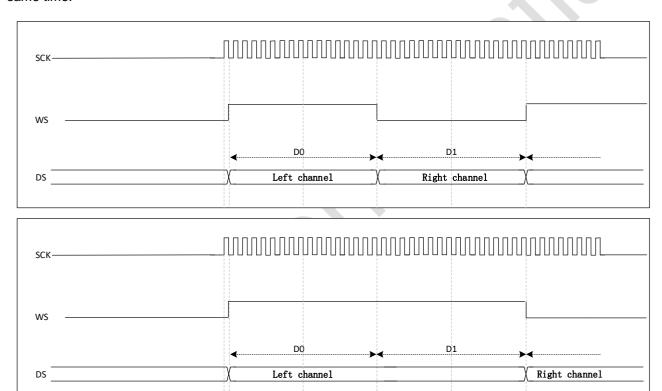

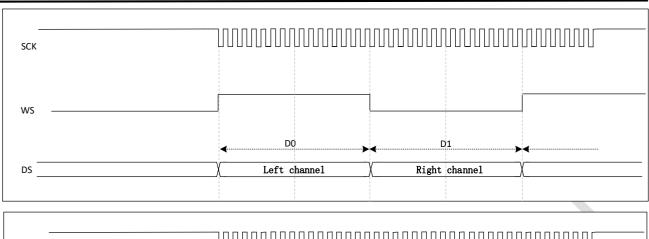

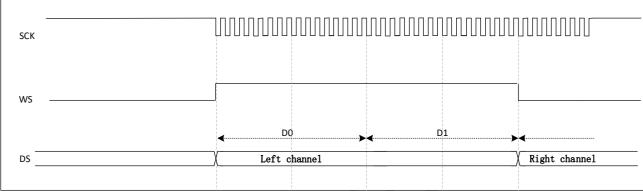

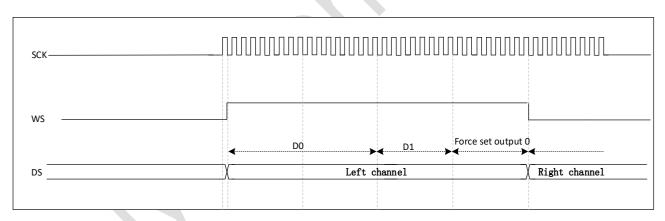

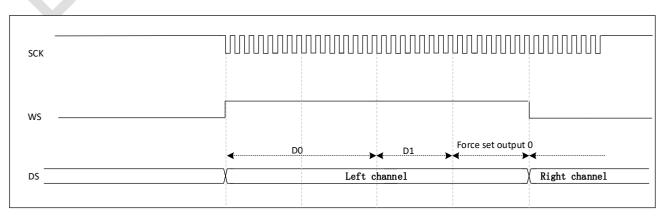

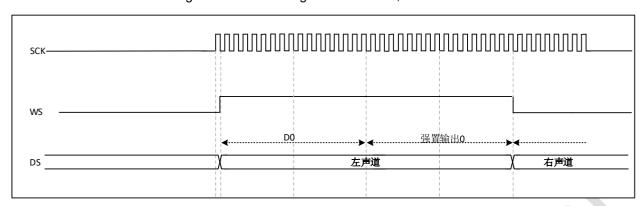

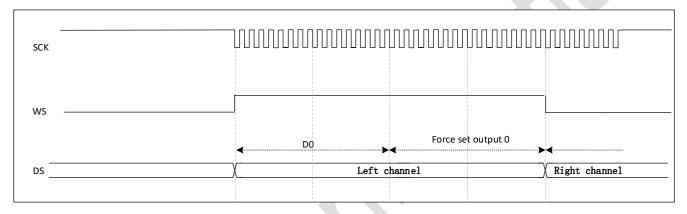

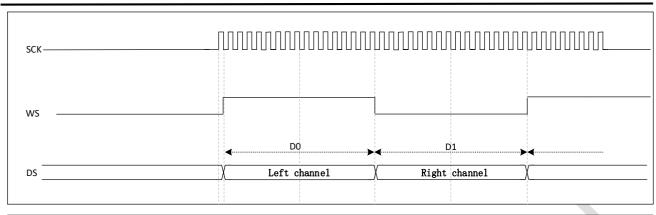

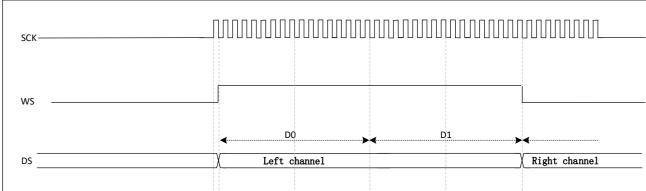

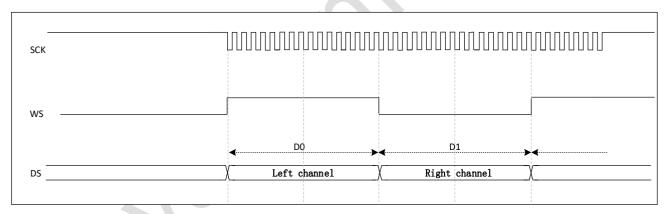

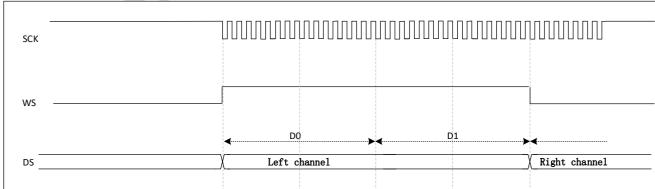

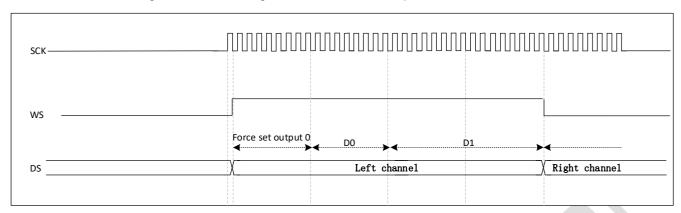

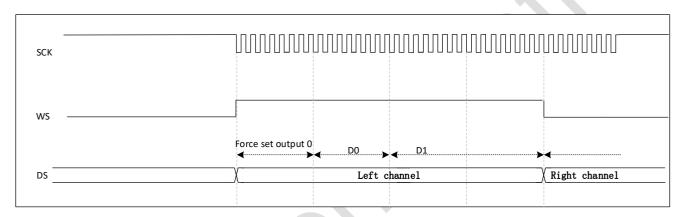

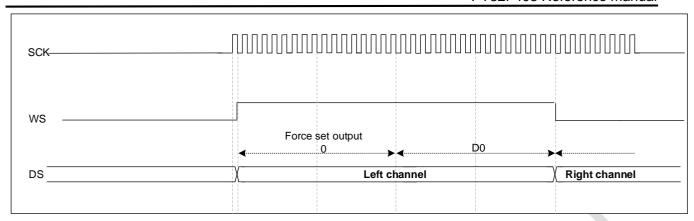

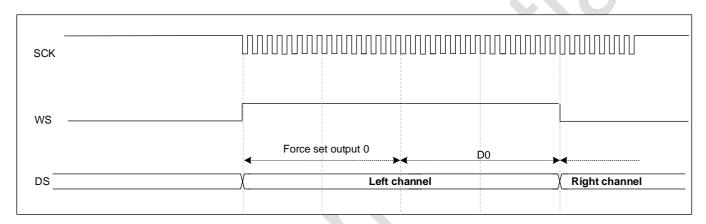

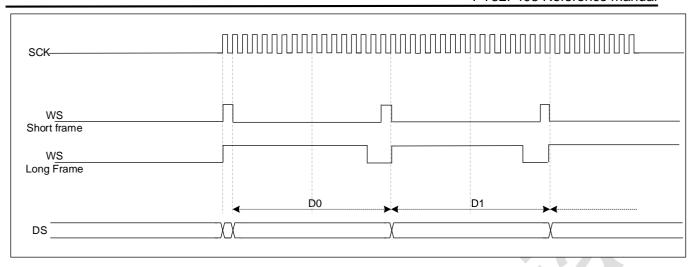

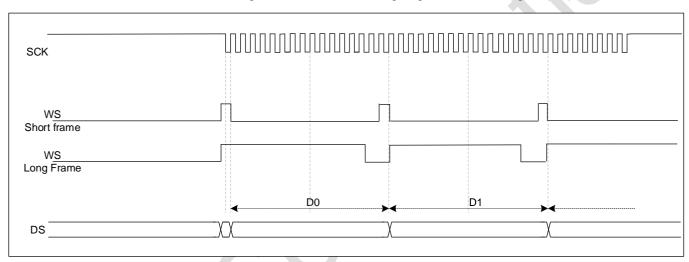

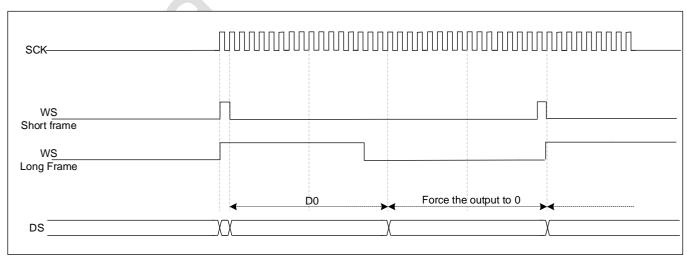

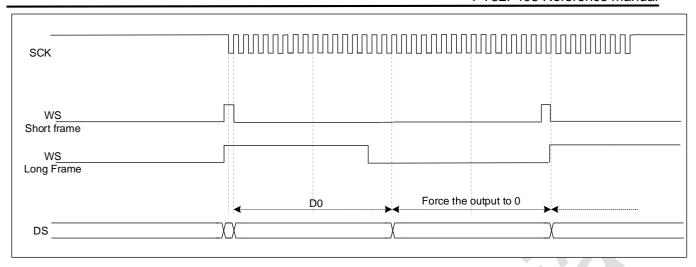

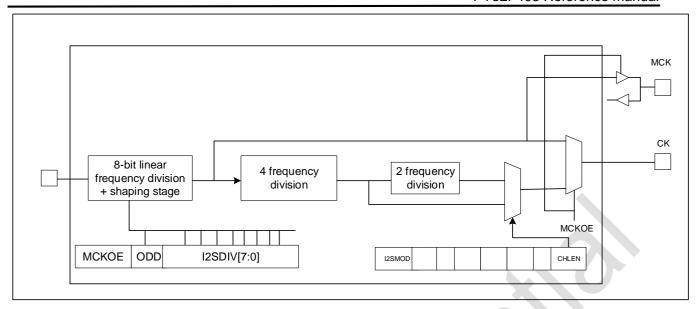

| 25.3.2.  | Audio Protocol                                           | . 645 |

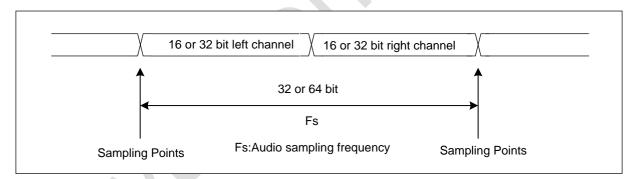

| 25.3.3.  | Clock                                                    | . 656 |

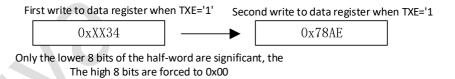

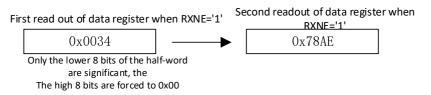

| 25.3.4.  | Send and Receive                                         | . 657 |

| 25.3.5.  | Logo position                                            | . 659 |

| 25.3.6.  | Interruption                                             | . 660 |

| 25.4. R  | egister Description                                      | . 660 |

| 25.4.1.  | SPI_CR1 register                                         | . 660 |

| 25.4.2.  | SPI_CR2 register                                         |       |

| 25.4.3.  | SPI_SR register                                          |       |

| 25.4.4.  | SPI_DR register                                          |       |

| 25.4.5.  | SPI_CRCPR register                                       |       |

| 25.4.6.  | SPI_RXCRCR register                                      |       |

| 25.4.7.  | SPI_TXCRCR register                                      |       |

| 25.4.8.  | SPI_I2S_CFGR register                                    |       |

| 25.4.9.  | SPI_I2SPR register                                       |       |

|          | SPI register map                                         |       |

|          |                                                          |       |

| 26. | Inter-               | integrated circuit (I2C) interface                          | 673 |

|-----|----------------------|-------------------------------------------------------------|-----|

|     |                      | ntroduction                                                 |     |

| _   | 26.1.1.              |                                                             |     |

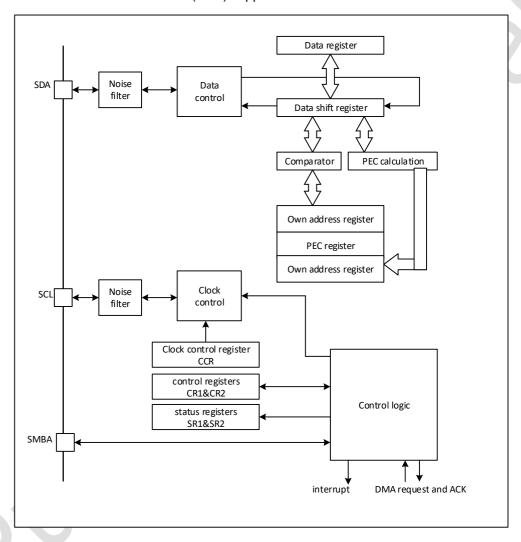

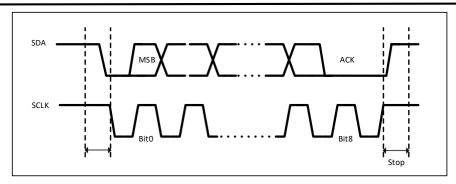

| 2   |                      | 2C Function Description                                     |     |

| _   | 26.2.1.              | Introduction                                                |     |

|     | 26.2.2.              | Packet Error Checking (PEC)                                 |     |

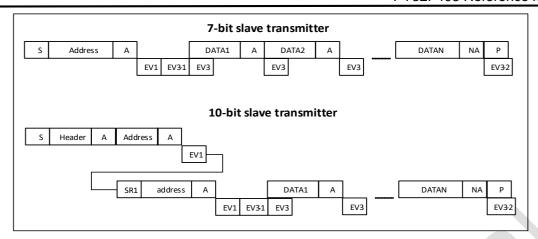

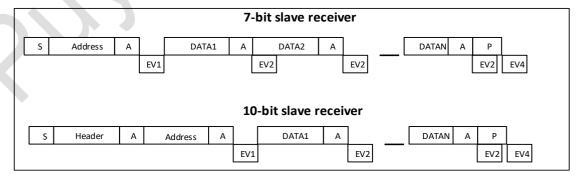

|     | 26.2.3.              | Slave mode                                                  |     |

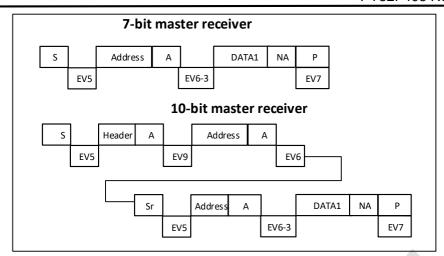

|     | 26.2.4.              | Master Mode                                                 |     |

|     | 26.2.5.              | Error status                                                |     |

|     | 26.2.6.              | DMA function                                                |     |

|     | 26.2.7.              | System Management Bus SMbus                                 |     |

| 2   |                      | Register Description                                        |     |

| _   | 26.3.1.              | I2C Control register 1 (I2C_CR1)                            |     |

|     | 26.3.2.              | I2C Control register 2 (I2C_CR2)                            |     |

|     | 26.3.3.              | I2C Own address register1 (I2C_OAR1)                        |     |

|     | 26.3.4.              | I2C own address register2(I2C_OAR2)                         |     |

|     | 26.3.5.              | I2C Data register(I2C_DR)                                   |     |

|     | 26.3.6.              | I2C Staus register (I2C_SR1)                                |     |

|     | 26.3.7.              | I2C Status register (I2C_SR2)                               |     |

|     | 26.3.8.              | I2C Clock control register(I2C_CCR)                         |     |

|     | 26.3.9.              | I2C TRISE register (I2C_TRISE)                              |     |

|     | 26.3.10.             | $\mathbf{c}$                                                |     |

| 27. |                      | ersal synchronous asynchronous receiver transmitter (USART) |     |

|     |                      | ntroduction                                                 |     |

|     | .7.1. II<br>27.1.1.  |                                                             |     |

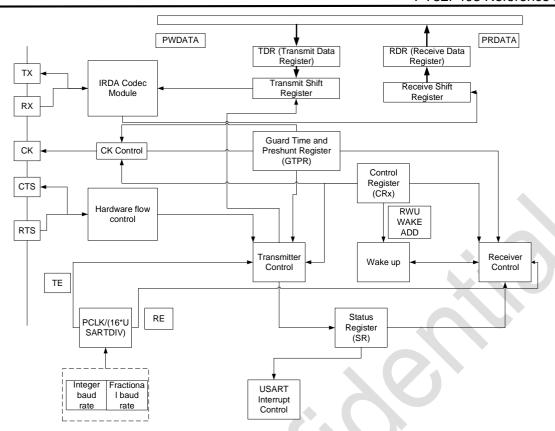

| 2   |                      | JSART Functional Description                                |     |

|     | 27.2.1.              |                                                             |     |

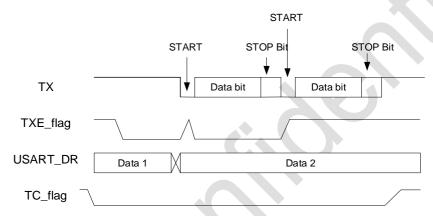

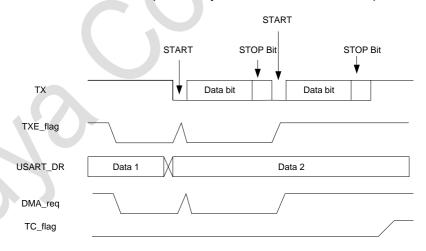

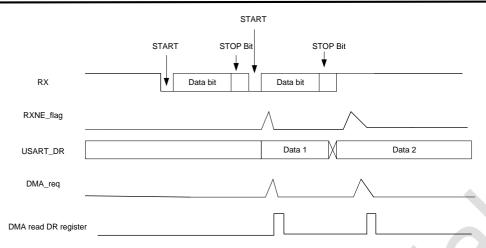

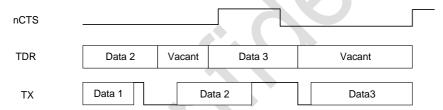

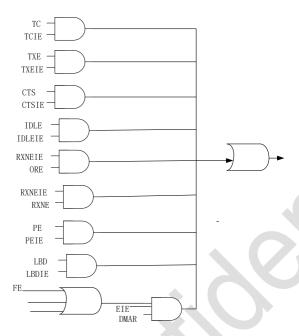

|     | 27.2.1.              | USART Transmit                                              |     |

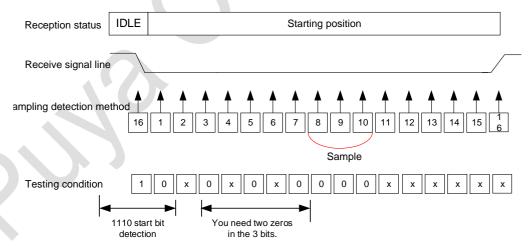

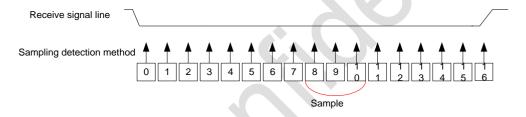

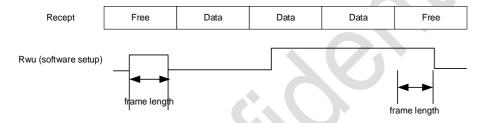

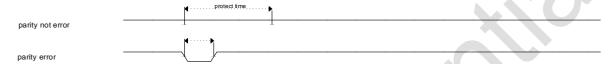

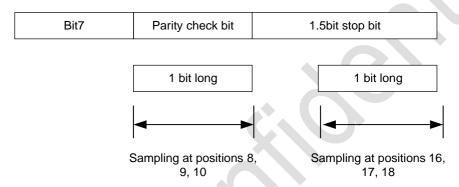

|     | 27.2.2.              | Data reception                                              |     |

|     | 27.2.3.              | Fractional baud rate generation                             |     |

|     | 27.2.4.              | USART receiver tolerates clock changes                      |     |

|     | 27.2.5.              | USART automatic baud rate detection                         |     |

|     |                      |                                                             |     |

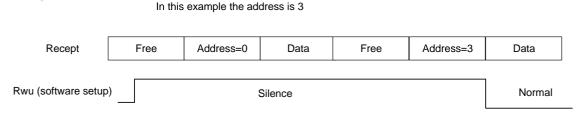

|     | 27.2.7.              | Multiprocessor communication                                |     |

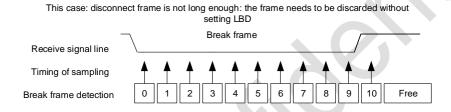

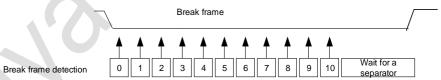

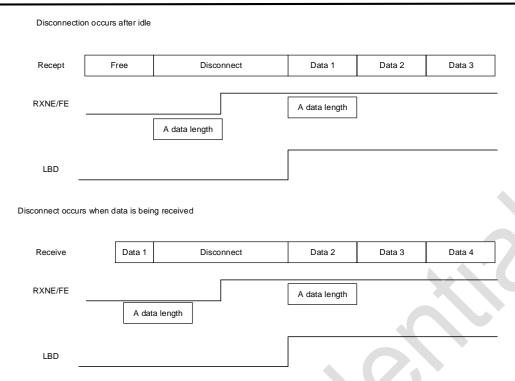

|     | 27.2.8.              | LIN (local area network) model                              |     |

|     | 27.2.9.              |                                                             |     |

|     | 27.2.10.             |                                                             |     |

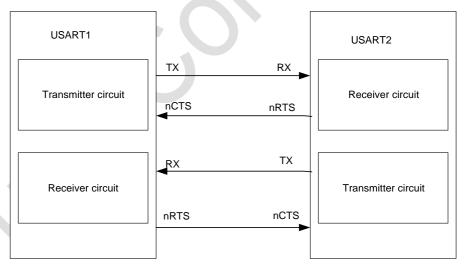

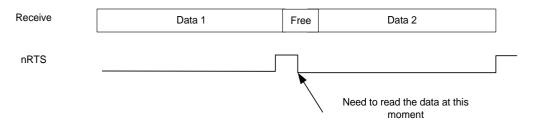

|     | 27.2.11.<br>27.2.12. |                                                             |     |

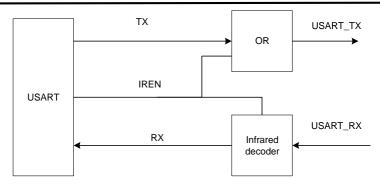

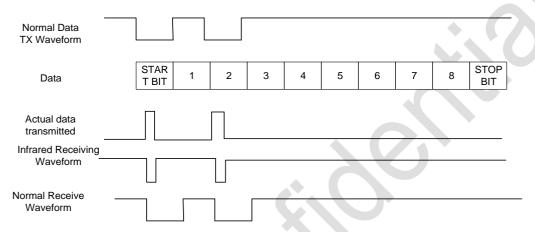

|     | 27.2.12.<br>27.2.13. | IrDA SIR ENDEC Function Module                              |     |

|     | 27.2.13.<br>27.2.14. |                                                             |     |

|     | 27.2.14.<br>27.2.15. |                                                             |     |

|     | 27.2.15.<br>27.2.16. |                                                             |     |

| 2   |                      |                                                             |     |

|     | .7.3. г<br>27.3.1.   | Register description                                        |     |

|     | _                    | Control Register (SR)                                       |     |

|     | 27.3.2.              | Data register (USART_DR)                                    |     |

|     | 27.3.3.              | Baud Rate Register (USART_BRR)                              |     |

|     | 27.3.4.<br>27.3.5.   | Control Register (USART_CR)                                 | 740 |

|     |                      |                                                             |     |

| 28. | 27.3.6.              | USART register map                                          |     |

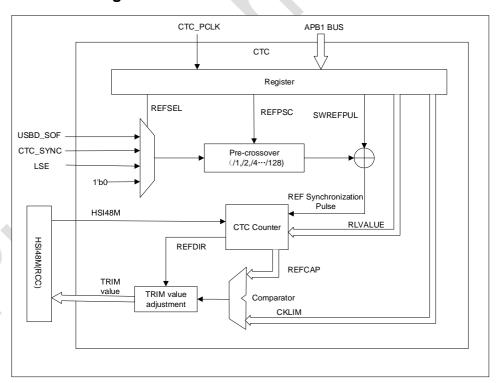

|     |                      | Calibration Controller (CTC)                                |     |

|     | 8.1. li<br>28.1.1.   | ntroduction                                                 |     |

|     |                      |                                                             |     |

| 2   | 28.1.2.<br>8.2. F    | Module block diagram                                        |     |

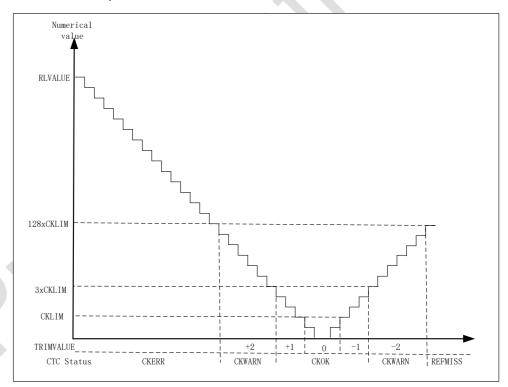

| 2   | .8.∠. F<br>28.2.1.   | Functional description                                      |     |

|     | 28.2.1.<br>28.2.2.   | REF Synchronized Pulse Generator                            |     |

|     |                      | CTC Calibration Counter.                                    |     |

|     | 28.2.3.              | Frequency evaluation and automatic calibration process      |     |

| ^   | 28.2.4.              | Software programming guide                                  | 740 |

| 2   |                      | Register description (base address 0x4000_C800)             |     |

|     | 28.3.1.              | Control register 0 (CTC_CTL0)                               |     |

|     | 28.3.2.              | Control register 1 (CTC_CTL1)                               |     |

|     | 28.3.3.<br>28.3.4.   | Status register (CTC_SR)Interrupt clear register (CTC_INTC) |     |

|     | ۷۵.۵.4.              | III.GITUPL OGAI IGGISIGI (OTO IINTO)                        | 101 |

| 28.3.5. CTC register map                                       | 752 |

|----------------------------------------------------------------|-----|

| 29. Debug support (DBG)                                        | 753 |

| 29.1. Introduction                                             | 753 |

| 29.1.1. Main features                                          | 753 |

| 29.2. Function description                                     | 753 |

| 29.2.1. Low-power mode is supported in debugging               | 753 |

| 29.3. Register baseaddr=0xE0042000                             | 753 |

| 29.3.1. ID code (DBGMCU_IDCODE) (0xE004_2000)                  | 753 |

| 29.3.2. Debug configuration register (DBGMCU_CR) (0xE004_2004) | 754 |

| 29.3.3. DBG register map                                       |     |

| 30. Version History                                            | 759 |

# 1. Introduction

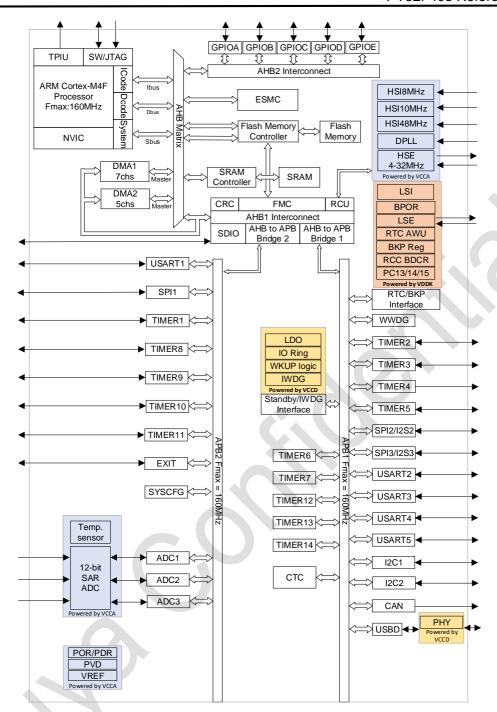

The system consists of the Cortex-M4 processor core, which includes SIMD's DSP enhancements and the Floating Process Unit (FPU) unit, which can be switched on or off depending on the configuration, but is supported by default for SIMD instructions. The on-chip Flash is used only as a read-only space for software instructions and data during system operation, with an instruction and data cache added to the system to increase the efficiency of the CM4, and an on-chip Flash with 128-bit data to reduce access time to the on-chip Flash. To reduce access time to the on-chip Flash, the on-chip Flash provides a 128-bit data read bit width. The Quad/Octal SPI Flash extends the system's non-volatile runnable storage while occupying only a small number of GPIO ports. The system includes DMA1 and 2 which can support up to 12 channels for direct data transfer between memory, peripherals including ADC, SDIO, I2S, I2C and USART.

The system includes two peripheral system buses, APB1 and APB2, with the same speed as the AHB bus. The peripherals include 17 timer units and 13 communication interface units. The former includes ten 16-bit timers, two 16-bit timers with PWM control, two watchdog timers, two basic timers and one systick timer. The latter includes two I2C interfaces, five USART interfaces, three SPI interfaces, a CAN bus controller, a USB 2.0 interface supporting full speed operation and an SDIO interface.

Figure 1-1 Module block diagram

# 2. System and memory architecture

The PY32F403XX family of devices is a 32-bit general purpose microcontroller based on the Arm® Cortex®-M4 processor. The Arm® Cortex®-M4 processor includes three AHB buses called the I-CODE bus, the D-Code bus and the system bus respectively. All memory accesses to the Cortex®-M4 processor are performed on these three buses, depending on the purpose and target memory space. The organisation of the memory is based on a Harvard structure, with pre-defined memory mappings and up to 4 GB of storage space, which fully guarantees system flexibility and scalability.

# 2.1. Arm® Cortex®-M4 Processor Introduction

The Cortex®-M4 processor is a 32-bit processor with low interrupt latency times and low cost debug features. The high level of integration and enhanced features make the Cortex™-M4 processor suitable for those market segments that require high performance and low power microcontrollers. The Cortex®-M4 processor is based on the Armv7 architecture and supports a powerful and scalable instruction set including general purpose data processing I/O control tasks, enhanced data processing bit field operations, DSP (Digital Signal Processing) and floating point instructions. Some of the system peripherals provided by the Cortex®-M4 are listed below:

- Internal bus matrix for interconnecting the I-Code bus, D-Code bus, system bus, private bus (PPB) and debug-only bus (AHB-AP);

- Nested Vector Interrupt Controller (NVIC);

- Flash Address Reload and Breakpoint Unit (FPB);

- Data Watchpoint and Trace Unit (DWT);

- Instruction Trace Macro Unit (ITM);

- Embedded Trace Macro Unit (ETM);

- Serial Line and JTAG Debug Interface (SWJ-DP);

- Trace Port Interface Unit (TPIU);

- Memory Protection Unit (MPU);

- Floating Point Unit (FPU).

# 2.2. System architecture

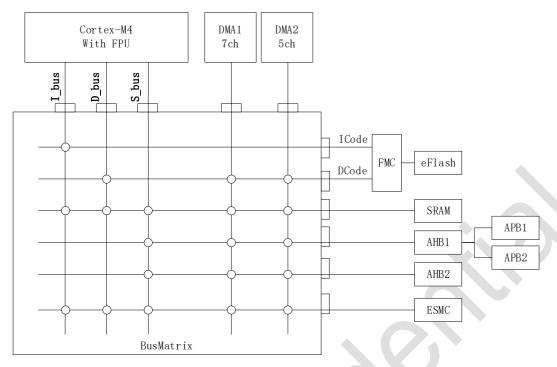

The system uses a 32-bit multi-layer AHB bus matrix that allows for parallel communication between multiple masters and multiple slaves:

- Five master buses:

- Cortex™-M4F core I-bus, D-bus and S-bus

- DMA1 memory bus

- DMA2 memory bus

- Five Controlled Buses:

- Internal Flash ICode bus

- Internal Flash DCode bus

- Internal SRAM bus

- AHB1 peripheral bus (including AHB to APB bus bridge and APB peripherals)

- AHB2 peripheral bus

#### ESMC

Figure 2-1 Bus Architecture

### 2.2.1. I\_bus

This bus is used to connect the instruction bus of the Cortex<sup>™</sup>-M4F core to the bus matrix. The kernel gets its instructions via this bus. This bus accesses the memory containing the code (internal Flash/SRAM or external memory via ESMC).

#### 2.2.2. D bus

This bus is used to connect the Cortex<sup>™</sup>-M4F data bus to the bus matrix. The kernel performs immediate number loading and debug accesses via this bus. This bus accesses memory containing code or data (internal Flash/SRAM or external memory via ESMC).

### 2.2.3. S\_bus

This bus is used to connect the system bus of the Cortex<sup>™</sup>-M4F core to the bus matrix. This bus is used to access data located in peripherals or SRAM. This bus accesses the 64 KB internal SRAM, the APB1 peripheral including the AHB peripheral, the APB2 peripheral and the external memory via the ESMC.

#### 2.2.4. DMA1/DMA2 BUS

This bus is used to connect the main DMA memory bus interface to the bus matrix. The DMA accesses via this bus are the 64KB internal SRAM, the APB1 peripheral including the AHB peripheral, the APB2 peripheral and the external memory via the ESMC.

#### 2.2.5. Bus Matrix

The bus matrix is used to manage the arbitration of accesses between master buses. Arbitration is performed using a round-robin scheduling algorithm. The system consists of five Master devices, I\_BUS, D\_BUS, S\_BUS, DMA1 and DMA2 of the ARM® Cortex™-M4, and four Slave devices, internal

Flash memory, internal SRAM, AHB peripherals (AHB2APB Bridge 1 for the peripherals and AHB2APB Bridge 2 for the AHB2APB Bridge 1 and AHB2APB Bridge 2), and ESMC.

### 2.2.6. AHB/APB bus bridge

With the AHB/APB bus bridge, a fully synchronous connection between the AHB bus and the APB bus is possible, allowing flexible selection of peripheral frequencies.

After each chip reset, all peripheral clocks are switched off (except for the SRAM and Flash interfaces). Before a peripheral can be used, its clock must be enabled in the RCC\_AHBXENR or RCC\_APBXENR registers.

# 2.3. Memory Organisation

#### 2.3.1. Introduction

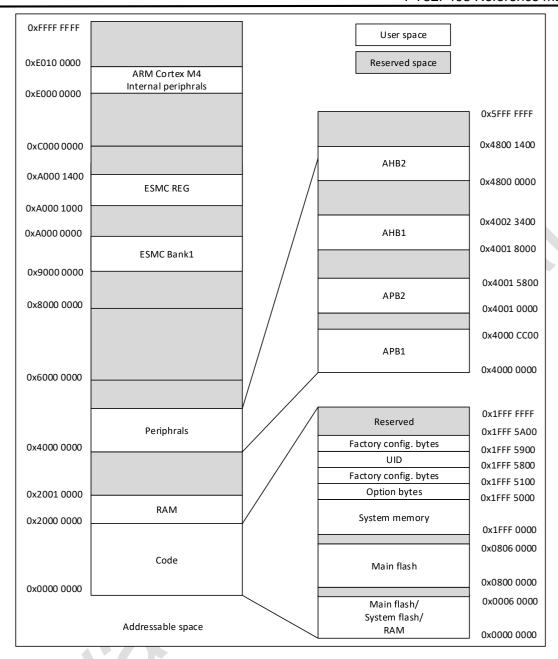

The Arm® Cortex®-M4 processor has a Harvard architecture that allows the use of mutually independent buses for reading instructions and loading/storing data. Instruction code and data are located in the same memory address space, but in different address ranges. Program memory, data memory, registers and I/O ports are all within the same linear 4 GB address space.

The individual bytes are encoded in memory in a small-end format. The lowest numbered byte in a word is considered the lowest valid byte for that word, while the highest numbered byte is considered the highest valid byte.

For more information on the mapping of peripheral registers, see the relevant section.

The addressable memory space is divided into 8 main blocks of 512 MB each.

#### 2.3.2. Memory Map

Figure 2-2 Memory Map

All other memory space not allocated to on-chip memory and peripherals is reserved address space. Refer to the table below for detailed memory and register space mapping.

The table below gives the peripherals available in the product and the corresponding address boundaries.

Table 2-1 Peripheral register address

| Memory start/stop address | Peripheral | Bus  | Register map |

|---------------------------|------------|------|--------------|

| 0xA000 1000 - 0xA000 13FF | ESMC       | AHB  |              |

| 0x4800 1400 - 0x5FFF FFFF | Reserve    |      |              |

| 0x4800 1000 - 0x4800 13FF | GPIOE      |      |              |

| 0x4800 0C00 - 0x4800 0FFF | GPIOD      | AHB2 |              |

| 0x4800 0800 - 0x4800 0BFF | GPIOC      |      |              |

| 0x4800 0400 - 0x4800 07FF | GPIOB      |      |              |

| Memory start/stop address | Peripheral                       | Bus  | Register map |

|---------------------------|----------------------------------|------|--------------|

| 0x4800 0000 - 0x4800 03FF | GPIOA                            |      |              |

| 0x4002 3400 - 0x47FF FFFF | Reserve                          |      |              |

| 0x4002 3000 - 0x4002 33FF | CRC                              |      |              |

| 0x4002 2400 - 0x4002 2FFF | Reserve                          |      |              |

| 0x4002 2000 - 0x4002 23FF | FMC                              |      |              |

| 0x4002 1400 - 0x4002 1FFF | Reserve                          |      |              |

| 0x4002 1000 - 0x4002 13FF | RCC                              | AHB1 |              |

| 0x4002 0800 - 0x4002 0FFF | Reserve                          |      |              |

| 0x4002 0400 - 0x4002 07FF | DMA2                             |      |              |

| 0x4002 0000 - 0x4002 03FF | DMA1                             |      |              |

| 0x4001 8400 - 0x4001 FFFF | Reserve                          |      |              |

| 0x4001 8000 - 0x4001 83FF | SDIO                             |      |              |

| 0x4001 5800 - 0x4001 7FFF | Reserve                          |      |              |

| 0x4001 5400 - 0x4001 57FF | TIMER11                          |      |              |

| 0x4001 5000 - 0x4001 53FF | TIMER10                          |      |              |

| 0x4001 4C00 - 0x4001 4FFF | TIMER9                           |      |              |

| 0x4001 4000 - 0x4001 4BFF | Reserve                          | *    |              |

| 0x4001 3C00 - 0x4001 3FFF | ADC3                             |      |              |

| 0x4001 3800 - 0x4001 3BFF | USART1                           |      |              |

| 0x4001 3400 - 0x4001 37FF | TIMER8                           | APB2 |              |

| 0x4001 3000 - 0x4001 33FF | SPI1                             |      |              |

| 0x4001 2C00 - 0x4001 2FFF | TIMER1                           |      |              |

| 0x4001 2800 - 0x4001 2BFF | ADC2                             |      |              |

| 0x4001 2400 - 0x4001 27FF | ADC1                             |      |              |

| 0x4001 0800 - 0x4001 23FF | Reserve                          |      |              |

| 0x4001 0400 - 0x4001 07FF | EXTI                             |      |              |

| 0x4001 0000 - 0x4001 03FF | SYSCFG                           |      |              |

| 0x4000 CC00 - 0x4000 FFFF | Reserve                          |      |              |

| 0x4000 C800 - 0x4000 CBFF | СТС                              |      |              |

| 0x4000 7800 - 0x4000 C7FF | Reserve                          |      |              |

| 0x4000 7400 - 0x4000 77FF | Reserve                          |      |              |

| 0x4000 7000 - 0x4000 73FF | PWR                              |      |              |

| 0x4000 6C00 - 0x4000 6FFF | ВКР                              |      |              |

| 0x4000 6800 - 0x4000 6BFF | Reserve                          |      |              |

| 0x4000 6400 - 0x4000 67FF | CAN                              |      |              |

| 0x4000 6000 - 0x4000 63FF | USBD/CAN share 512 bytes of SRAM | APB1 |              |

| 0x4000 5C00 - 0x4000 5FFF | USBD                             |      |              |

| 0x4000 5800 - 0x4000 5BFF | I2C2                             |      |              |

| 0x4000 5400 - 0x4000 57FF | I2C1                             |      |              |

| 0x4000 5000 - 0x4000 53FF | UASRT5                           |      |              |

| 0x4000 4C00 - 0x4000 4FFF | UASRT4                           |      |              |

| 0x4000 4800 - 0x4000 4BFF | USART3                           |      |              |

| 0x4000 4400 - 0x4000 47FF | USART2                           |      |              |

| Memory start/stop address | Peripheral | Bus | Register map |

|---------------------------|------------|-----|--------------|

| 0x4000 4000 - 0x4000 43FF | Reserve    |     |              |

| 0x4000 3C00 - 0x4000 3FFF | SPI3/I2S   |     |              |

| 0x4000 3800 - 0x4000 3BFF | SPI2/I2S   |     |              |

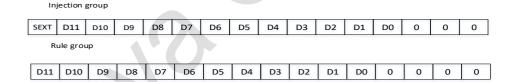

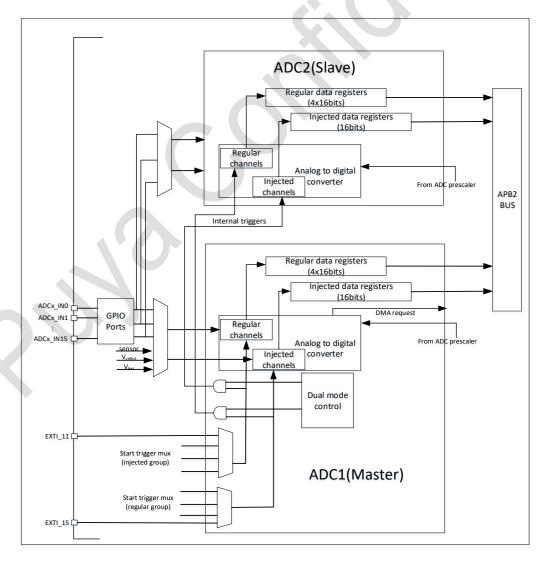

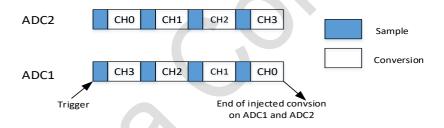

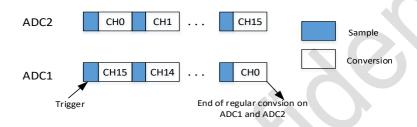

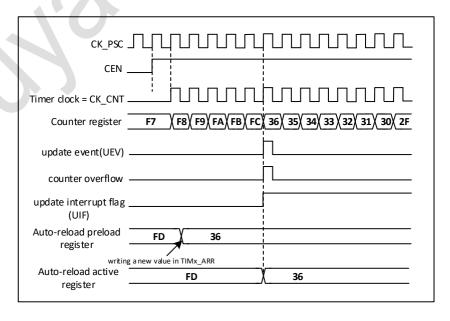

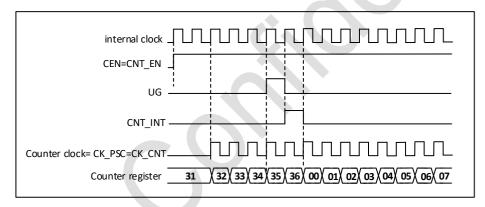

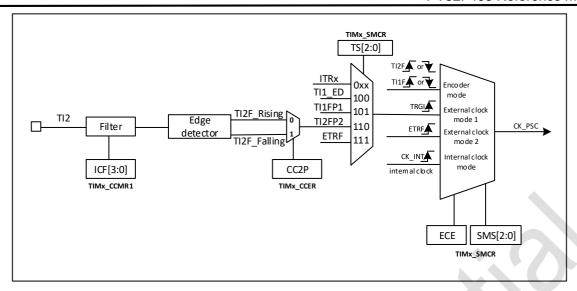

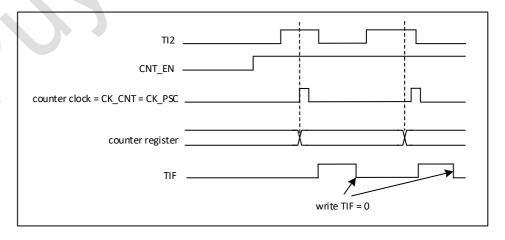

| 0x4000 3400 - 0x4000 37FF | Reserve    |     |              |